-If You Didn't Get This From My Site, Then It Was Stolen From... www.SteamPoweredRadio.Com

LYNN TAYLOR

0317

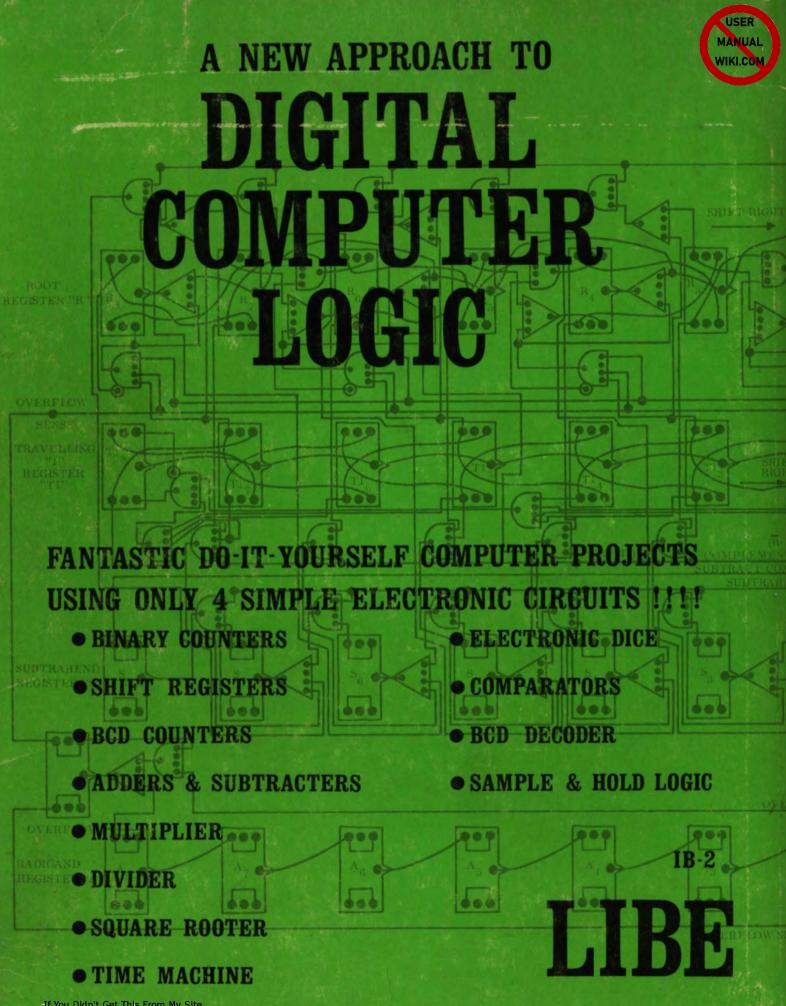

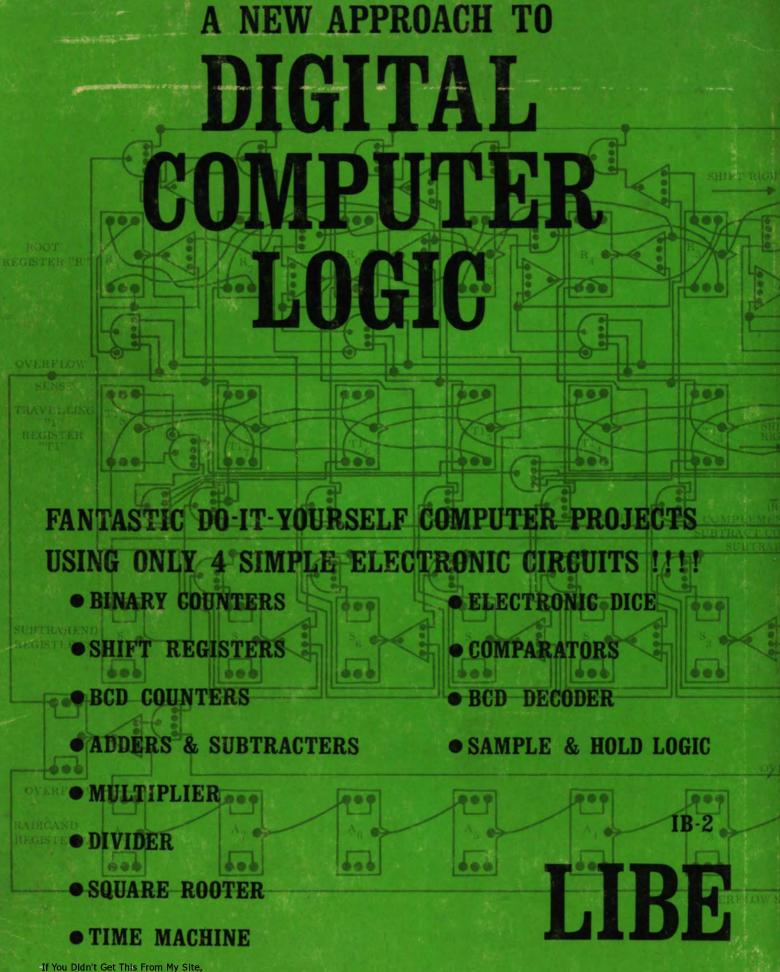

# A NEW APPROACH TO

# DIGITAL COMPUTER LOGIC

by

Burt Libe

Copyright © 1968, 1970

by

Libe Company and Burt Libe

All rights reserved under International and Pan-American Copyright Conventions. No reproduction of this book in whole or in part may be made without written permission of the publisher. Quotations of ten lines or less are excepted, provided acknowledgement is given.

Printed in the United States of America

Library of Congress Catalog Card No.

Published by:

LIBE COMPANY P.O. BOX 1196 LOS ALTOS, CALIFORNIA 94022 This book is for those who need a thorough basic discussion of digital computers and the binary number system. It is intended as a key to unlock the door to a fascinating world of the electronic computer circuits!!

| 1     | INTRODUCTION                                              |

|-------|-----------------------------------------------------------|

| 2     | LOGIC OPERATIONS, NOTATION, AND SYMBOLISM                 |

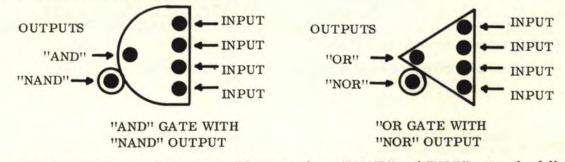

| 2.1   | "AND" LOGIC OPERATION                                     |

| 2.2   | "OR" LOGIC OPERATION                                      |

| 2.3   | "SUM" LOGIC OPERATION                                     |

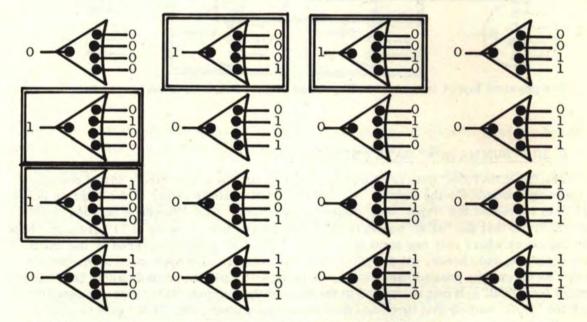

| 2.4   | "EOR" (EXCLUSIVE "OR") LOGIC OPERATION                    |

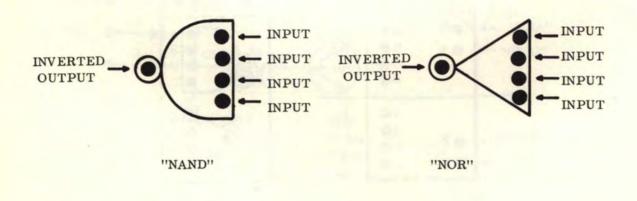

| 2.5   | "NAND" LOGIC OPERATION                                    |

| 2.6   | "NOR" LOGIC OPERATION                                     |

| 2.7   | FACTUAL EXAMPLES - THE BOOLEAN APPROACH                   |

| 2.8   | BINARY NUMBER "FACT" REPRESENTATION                       |

| 2.9   | LOGIC PARENTHESES AND BRACKETS                            |

| 3     | FUNDAMENTAL LOGIC THEOREMS, LAWS, AND IDENTITIES          |

| 3.1   | DEMORGAN'S THEOREMS                                       |

| 3.2   | COMMUTATIVE LAWS                                          |

| 3.3   | ASSOCIATIVE LAWS                                          |

| 3.4   | DISTRIBUTIVE LAWS                                         |

| 3.5   | FUNDAMENTAL IDENTITIES                                    |

| 3.6   | NEGATION AND DOUBLE NEGATION                              |

| 3.7   | SPECIAL IDENTITIES                                        |

| 3.8   | ADDITION IDENTITIES                                       |

| 4     | TRUTH TABLES                                              |

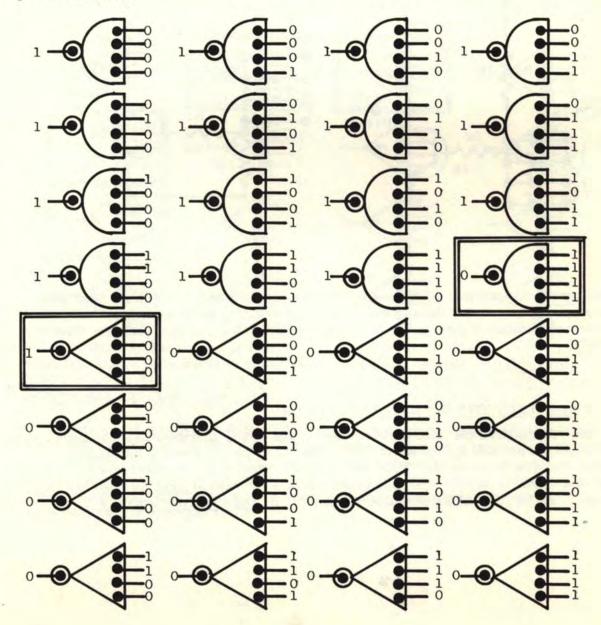

| 4.1   | LOGIC OPERATOR TRUTH TABLE REPRESENTATIONS                |

| 4.2   | PROOF OF DEMORGAN'S THEOREMS BY TRUTH TABLES              |

| 4.3   | PROOF OF DISTRIBUTIVE LAWS BY TRUTH TABLES                |

| 4.4   | PROOF OF FUNDAMENTAL IDENTITIES BY TRUTH TABLES           |

| 4.5   | PROOF OF ADDITION IDENTITIES BY TRUTH TABLES              |

| 5     | ELECTRONIC COMPUTER LOGIC NOTATION                        |

| 5.1   | EXAMPLES OF ELECTRONIC COMPUTER LOGIC EXPRESSIONS         |

| 6     | THE BINARY NUMBER SYSTEM                                  |

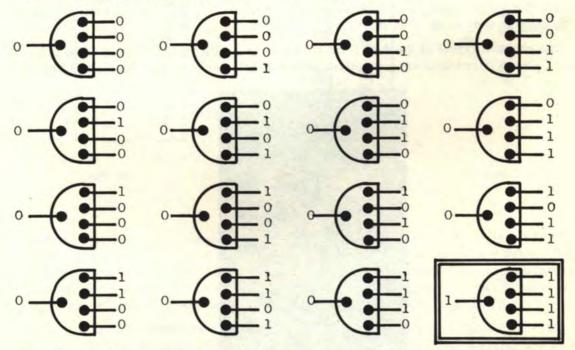

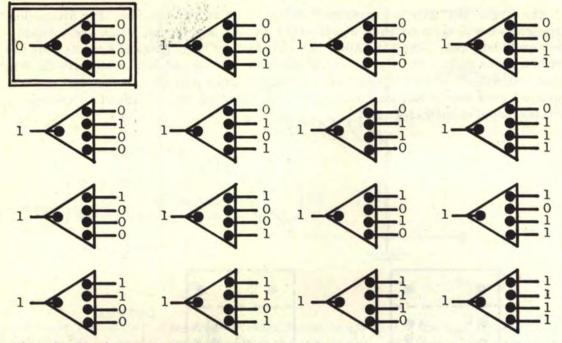

| 6.1   | TRUTH TABLES AND THE BINARY COUNT                         |

| 6.2   | BINARY ADDITION                                           |

| 6.3   | BINARY SUBTRACTION                                        |

| 6.4   | BINARY MULTIPLICATION                                     |

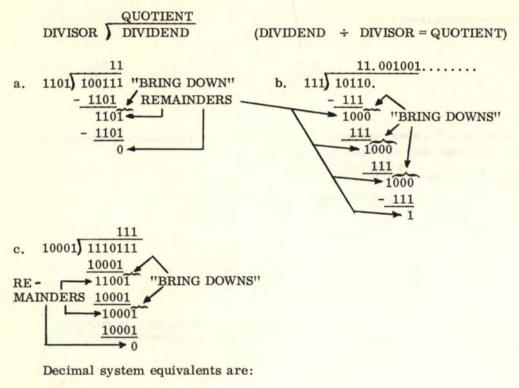

| 6.5   | BINARY DIVISION                                           |

| 6.6   | BINARY FRACTIONALS                                        |

| 6.6.1 | CONVERSION FROM DECIMAL FRACTIONALS TO BINARY FRACTIONALS |

| 6.6.2 | CONVERSION FROM BINARY FRACTIONALS TO DECIMAL FRACTIONALS |

| 6.7   | BINARY FRACTIONS                                          |

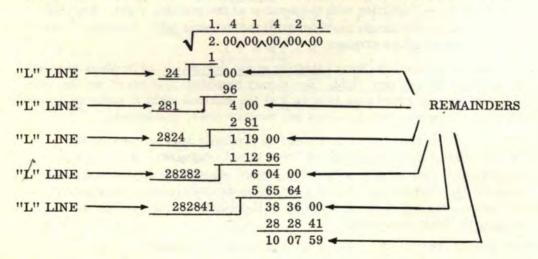

| 6.8   | SQUARE ROOTS                                              |

| 6.8.1 | EXTRACTING THE SQUARE ROOT                                |

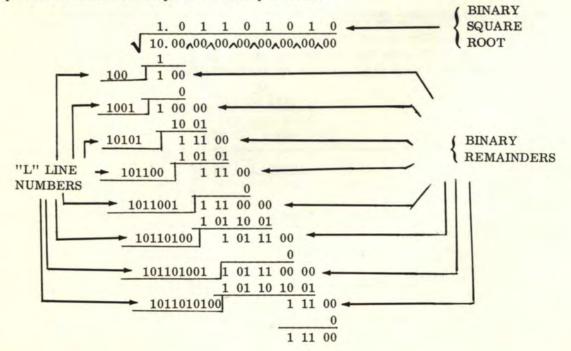

| 6.8.2 | THE BINARY SQUARE ROOT                                    |

| 6.9   | ROUNDING "UP" AND ROUNDING "DOWN"                         |

| 6.9.1 | BINARY "ROUNDING OFF"                                     |

| 6.10  | THE BINARY COMPLEMENT                                     |

| 7     | BINARY ELECTRONIC COMPUTER CIRCUITS                       |

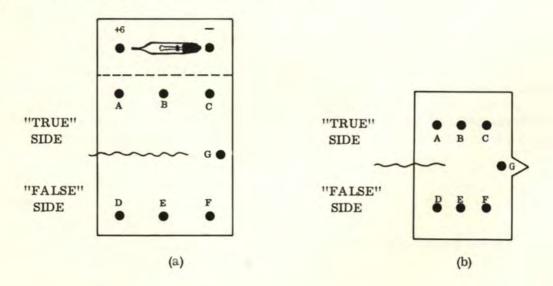

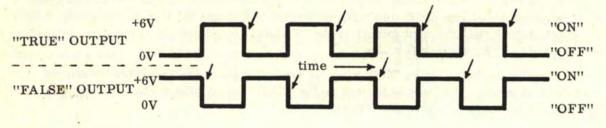

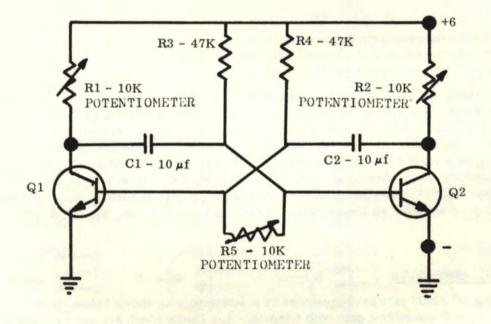

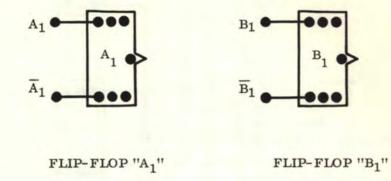

| 7.1   | THE FLIP-FLOP                                             |

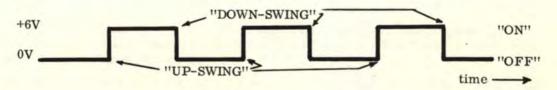

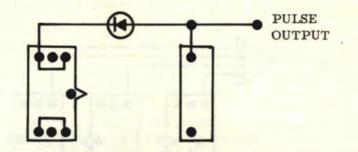

| 7.2   | THE PULSE GENERATOR                                       |

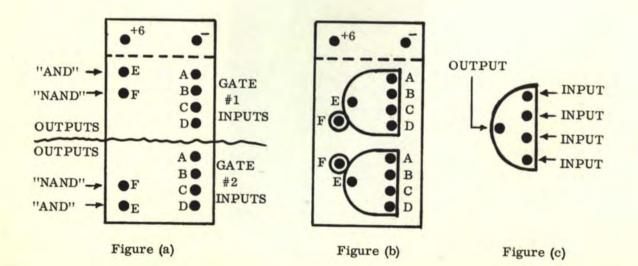

| 7.3   | LOGIC GATES                                               |

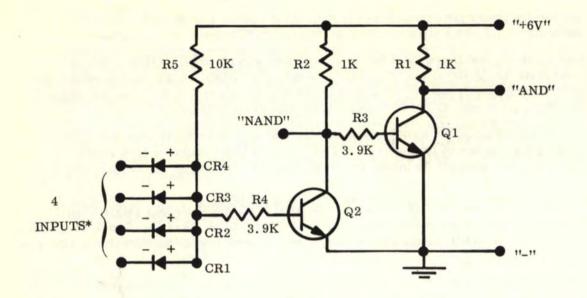

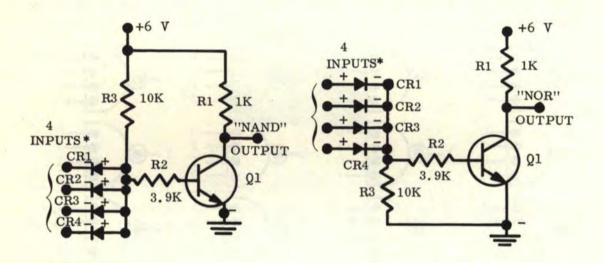

| 7.3.1 | THE "AND" GATE                                            |

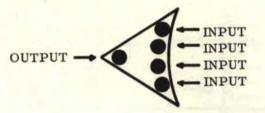

| 7.3.2 | THE "OR" GATE                                             |

#### TABLE OF CONTENTS (Continued)

11-

|         | TABLE OF CONTENTS (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

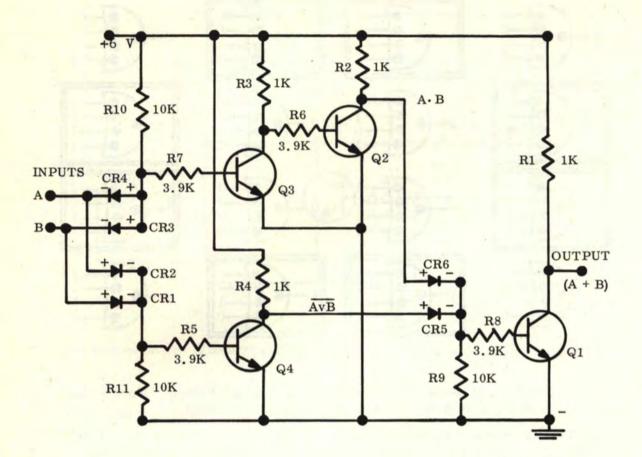

| 7.3.3   | THE "AND" AND "OR" GATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

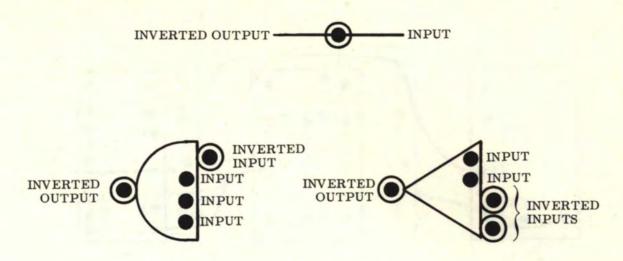

| 7.3.4   | NEGATIVE "AND" AND "OR" GATES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

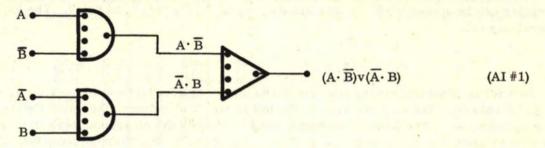

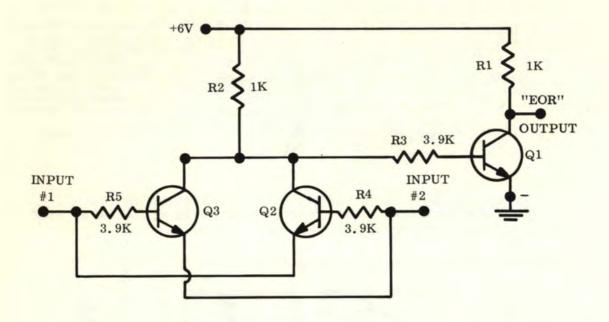

| 7.3.5   | THE "EXCLUSIVE OR" GATE ("EOR" GATE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

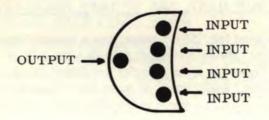

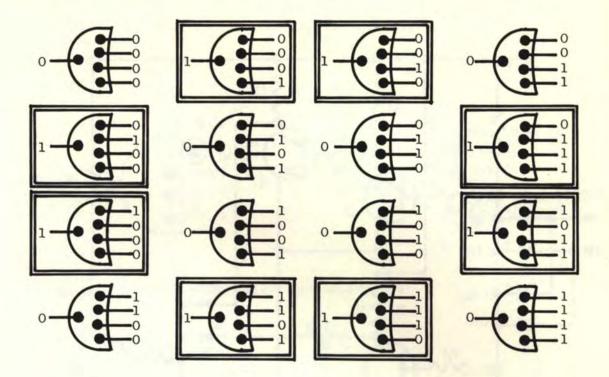

| 7.3.6   | THE "SUMMATION" GATE ("SUM" GATE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

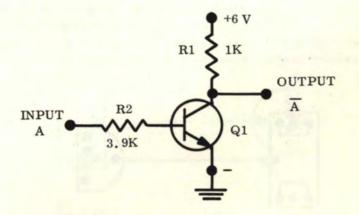

| 7.3.7   | THE "INVERTER" GATE ("NOT" GATE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

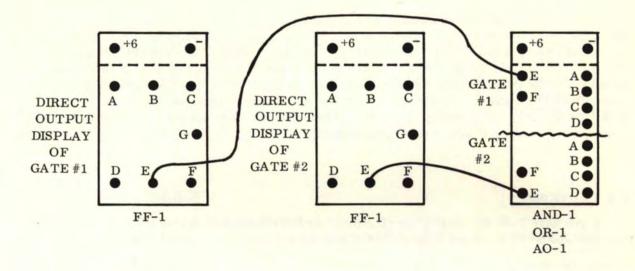

| 7.4     | GATE OUTPUT "TRIGGERING" AND DIRECT DISPLAY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | State and the state of the stat |

| 8       | ELECTRONIC COMPUTER CIRCUIT OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8.1     | CAUTIONS!!!!                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

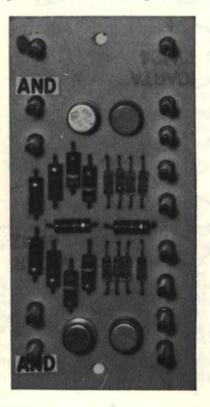

| 8.2     | PHYSICAL LAYOUT, MOUNTING, AND CONNECTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8.2.1   | MOUNTING BOARDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8.2.2   | WIRES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8.2.3   | LABELS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

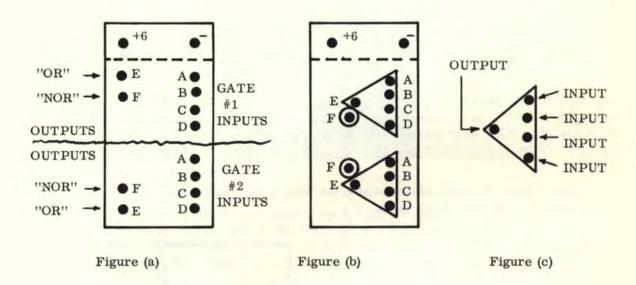

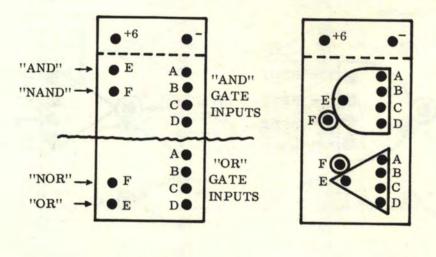

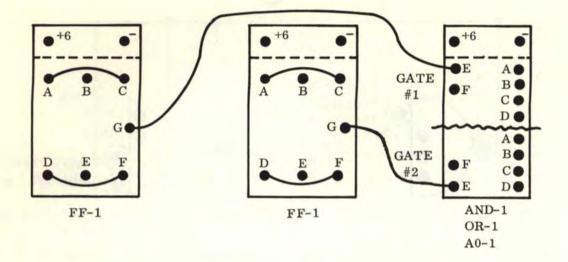

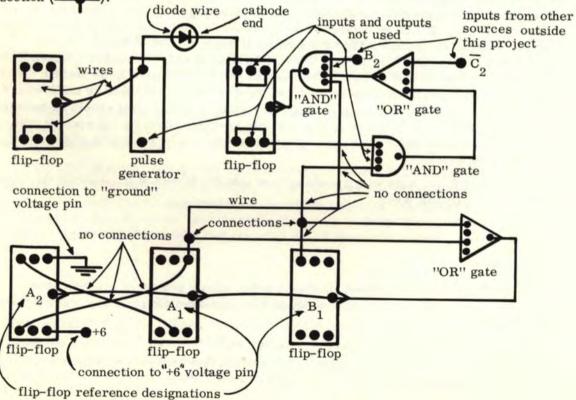

| 8.3     | LOGIC DIAGRAMS AND WIRING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

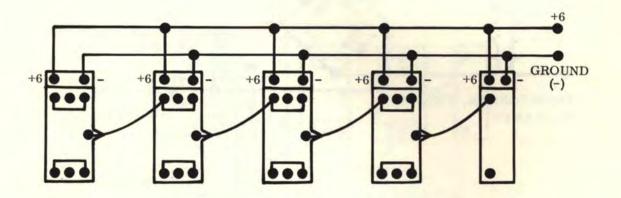

| 8.3.1   | POWER PIN CONNECTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

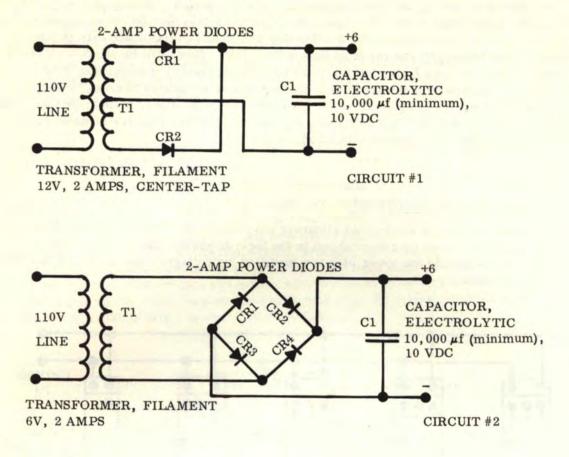

| 8.4     | POWER SOURCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8.5     | SENSES AND COMMANDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8.6     | SET AND RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8.7     | INTRINSIC PROBLEMS AND DEBUGGING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8.8     | CARE AND REPAIR OF UNITS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9       | BASIC NON-GATED COMPUTER PROJECTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

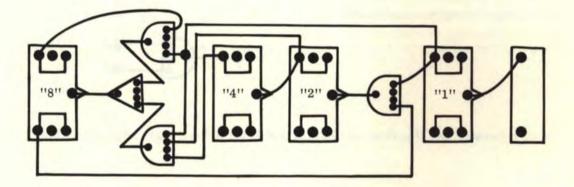

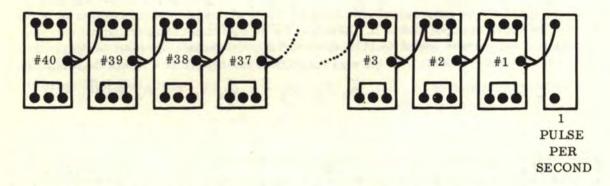

| 9.1     | THE BINARY "UP" COUNTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9.2     | THE BINARY "DOWN" COUNTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

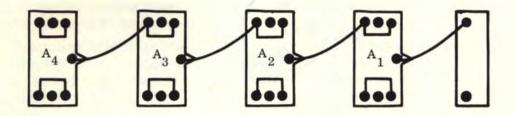

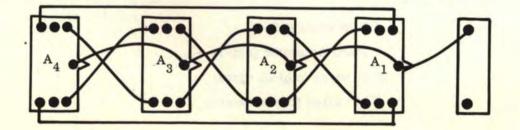

| 9.3     | THE BINARY SHIFT REGISTER (LEFT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

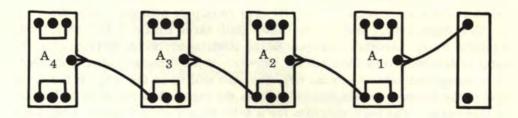

| 9.4     | THE BINARY SHIFT REGISTER (RIGHT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9.5     | THE COMPLEMENTARY TRANSFORMATION REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

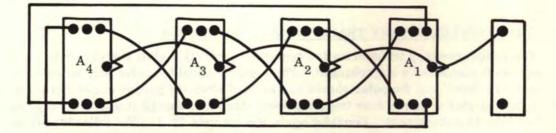

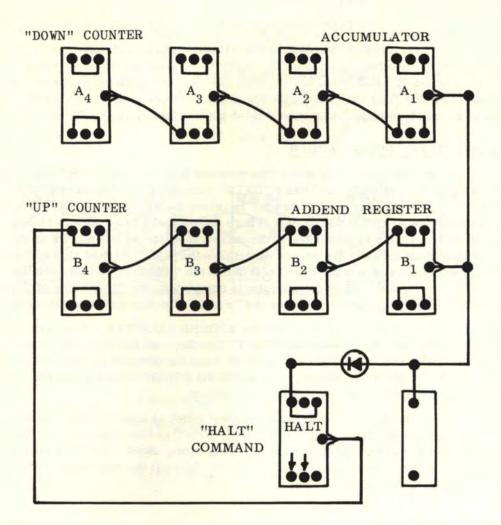

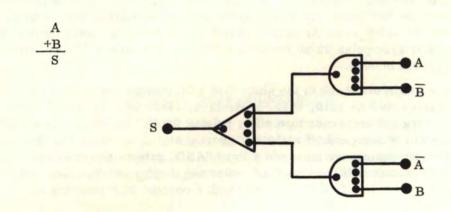

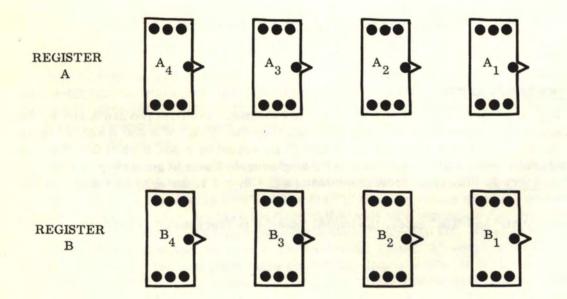

| 9.6     | THE COMPLEMENTART TRANSFORMATION REGISTER<br>THE NON-GATED BINARY ADDER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

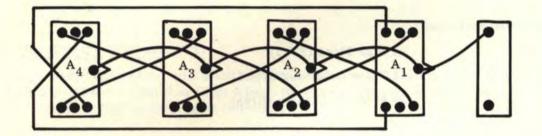

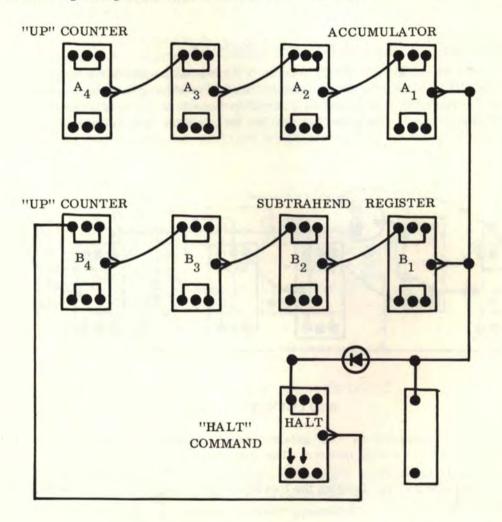

| 9.7     | THE NON-GATED BINARY SUBTRACTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.1     | THE NON-GATED BINART SUBTRACTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

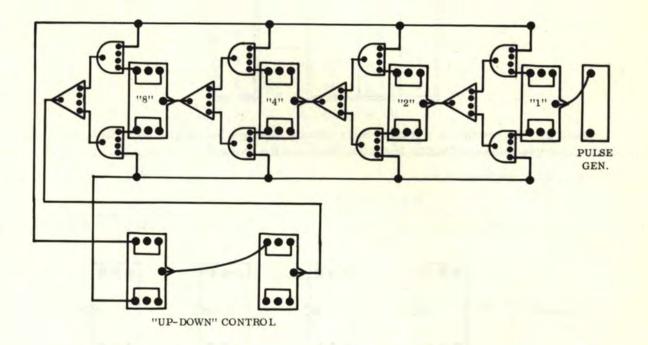

| 10      | ADVANCED COMPUTER PROJECTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

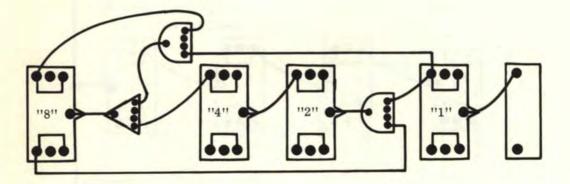

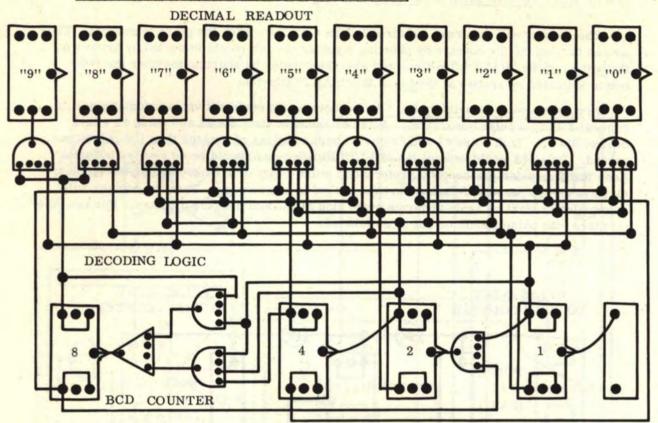

| 10.1    | THE BINARY CODED DECIMAL (BCD) COUNTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

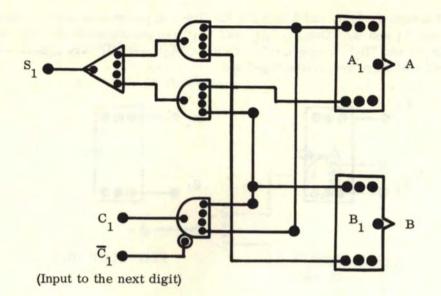

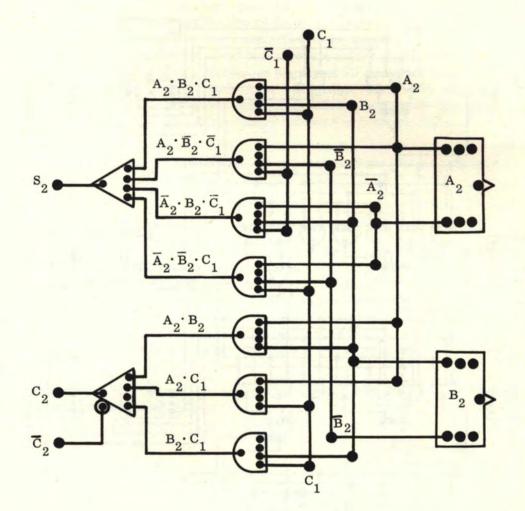

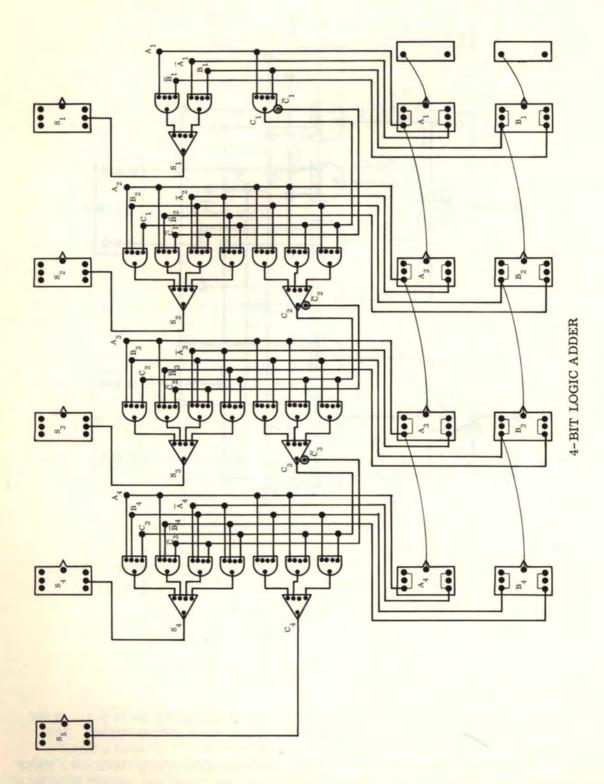

| 10.2    | THE LOGIC ADDER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

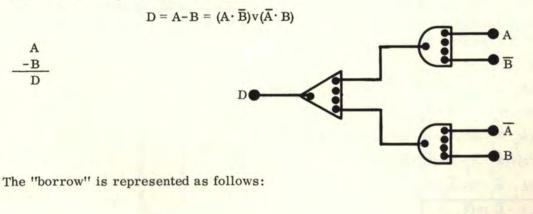

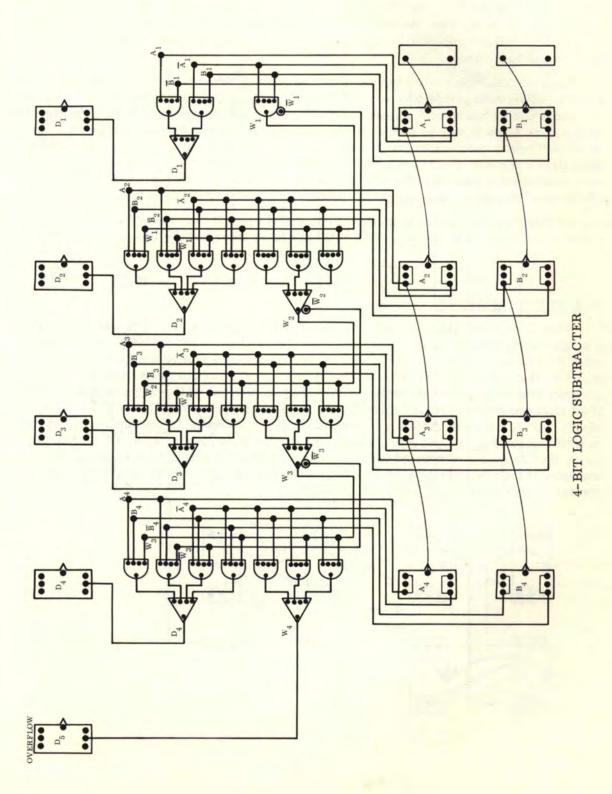

| 10.3    | THE LOGIC SUBTRACTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

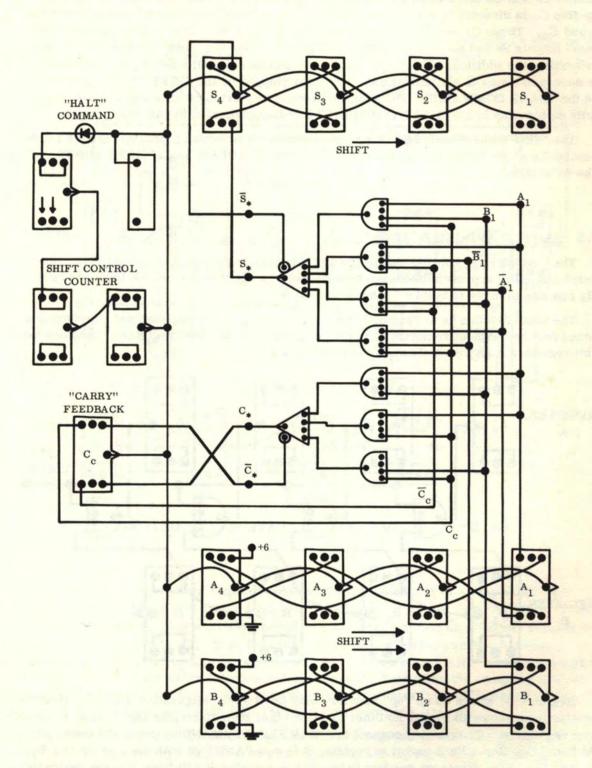

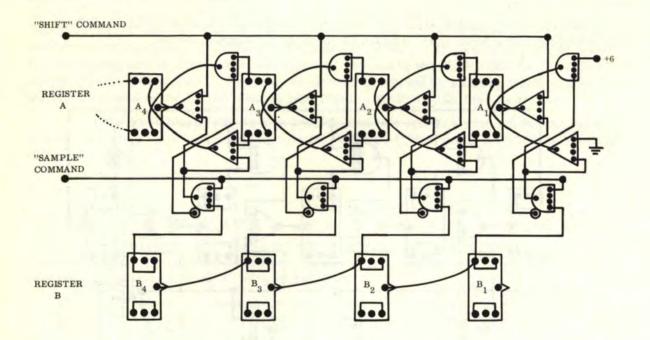

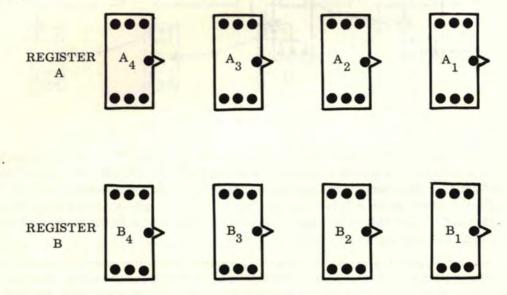

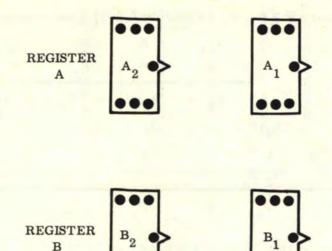

| 10.4    | THE SHIFT ADDER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

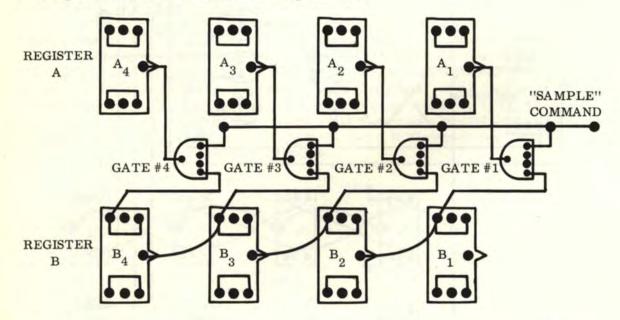

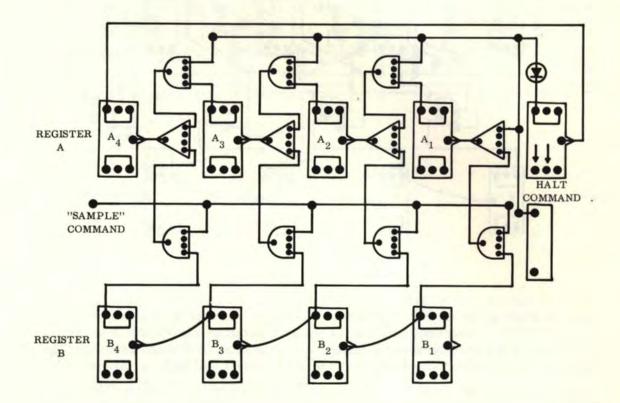

| 10.5    | "SAMPLE-AND-HOLD" LOGIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |