# PHASE-LOCKED LOOP DATA BOOK

First in Quality... First in Service • Custom, Semi-custom and Standard IC's

If You Didn't Get This From My Site, Then It Was Stolen From... www.SteamPoweredRadio.Com

# Introduction

This data book contains a complete summary of technical data and information covering Exar's complete line of Phase Locked Loop (PLL) IC products. Each of the products presented in this Data Book covers a wide range of applications which will greatly simplify most system designs. To help the designer to find the right devices for his applications, a number of convenient cross-reference charts are also included which show the key features of each of the products discussed, in terms of different classes of applications.

### EXPERIENCE AND PRODUCTS

Exar's innovativeness, product quality and responsiveness to customer needs have been the key to its success. Exar today offers a broad line of linear and interface circuits. In the field of standard linear IC products, Exar has extended its circuit technological leadership into the areas of communications and control circuits. Today Exar has one of the most complete lines of IC oscillators, timing circuits, and phase-locked loops in the industry. Exar also manufactures a large family of telecommunication circuits such as tone decoders, compandors, modulators, PCM repeaters, and FSK Modem Circuits. In the field of industrial control circuits, Exar manufactures a broad line of quad and dual operational amplifiers, voltage regulators, radio-control and servo driver IC's, and power circuits.

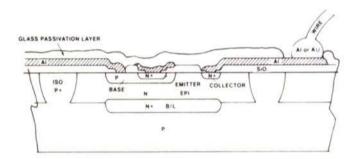

Exar's experience and expertise in the area of bipolar IC technology extends both into custom and standard IC products. In the area of custom IC's, Exar has designed, developed, and manufactured a wide range of full-custom monolithic circuits, particularly for applications in the areas of telecommunications, consumer electronics, and industrial controls.

In addition to the full-custom capability, Exar also offers a unique semi-custom IC development capability for lowto medium-volume custom circuits. This semi-custom program is intended for those customers seeking cost-effective solutions to reduce component count and board size in order to compete more effectively in a changing marketplace. The program allows a customized monolithic IC to be developed with a turnaround time of several weeks at a small fraction of the cost of a full-custom development program.

# EXCELLENCE IN ENGINEERING

Exar quality starts in Engineering where highly qualified people are backed up with the advanced instruments and facilities needed for design and manufacture of custom, semi-custom, and standard integrated circuits. Exar's engineering and facilities are geared to handle all three classes of IC design: (1) semi-custom design programs programs using Exar's bipolar and 1<sup>2</sup>L master chips; (2) full-custom IC design; (3) development and highvolume production of standard products.

Exar reserves the right to make changes at any time in order to improve design and to supply the best product possible. Some of the challenging and complex development programs successfully completed by Exar include analog compandors and PCM repeaters for telecommunication, electronic-injection, anti-skid braking systems and voltage regulators for automotive electronics, digital voltmeter circuits, 40 MHz frequency synthesizers, high-current and high-voltage display and relay driver IC's, and many others.

# NEW TECHNOLOGIES

Through company sponsored research and development activities, Exar constantly stays abreast of all technology areas related to changing customer needs and requirements. Exar has recently completed development efforts in Integrated Injection Logic ( $1^2L$ ) technology, which offers unique advantages in the area of low-power, high-density logic arrays. Exar has a complete design engineering group dedicated to this new technology, and is currently supplying over twenty different custom and semi-custom  $1^2L$  products.

# FIRST IN QUALITY

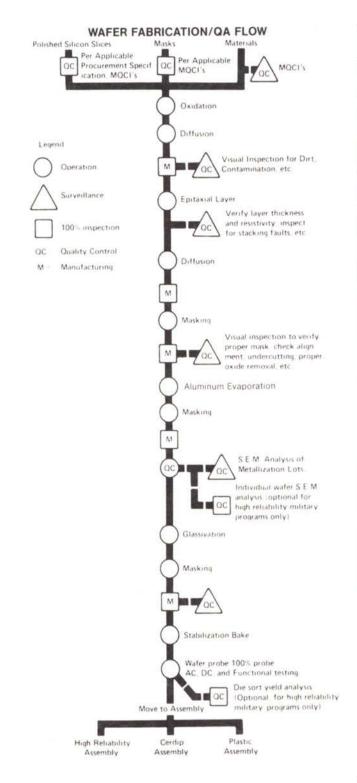

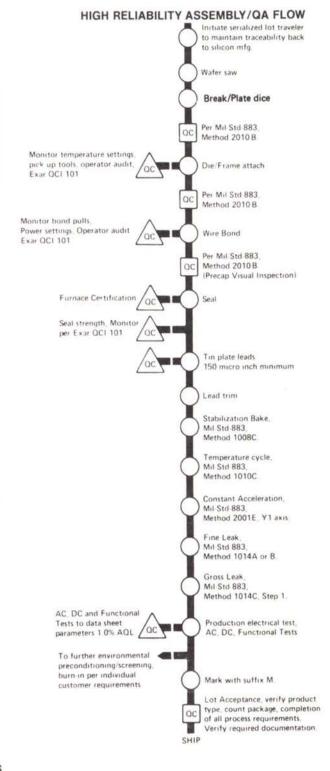

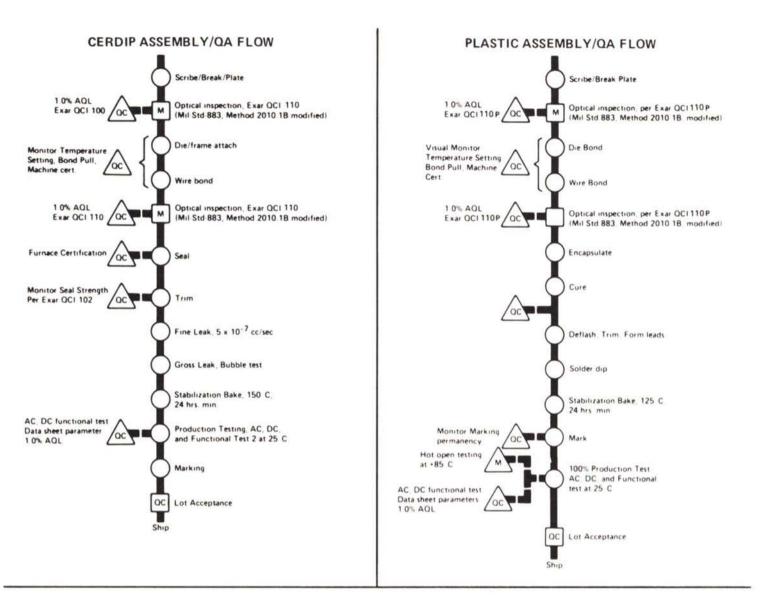

From incoming inspection of all materials to the final test of the finished goods, Exar performs sample testing of each lot to ensure that every product meets Exar's high quality standards. Exar's manufacturing process is inspected or tested in accordance with its own stringent Quality Assurance Program, which is in compliance wit MIL-Q9858A. Additional special screening and testing can be negotiated to meet individual customer requirements.

Throughout the wafer fab and assembly process, the latest scientific instruments, such as scanning electron microscopes, are used for inspection, and modern automated equipment is used for wafer probe, AC, DC, and functional testing. Environmental and burn-in testing of finished products is also done in-house. For special environmental or high reliability burn-in tests outside testing laboratories are used to complement Exar's own extensive inhouse facilities.

# FIRST IN SERVICE

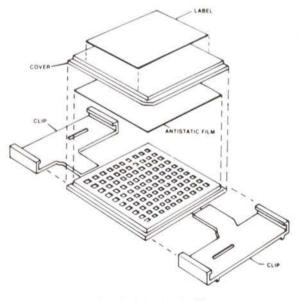

Exar has the ability and flexibility to serve the customer in a variety of ways from wafer fabrication to full parametric selection of assembled units for individual customer requirements. Special marking, special packaging and military screening are only a few of the service options available from Exar. We are certain that Exar's service is flexible enough to satisfy 99% of customer needs. The company has a large staff of Applications Engineers to assist the customer in the use of the product and to handle any request, large or small.

Exar cannot assume any responsibility for any circuits shown or represent that they are free from patent infringement.

# **Table of Contents**

| n |   | _ |   |

|---|---|---|---|

| ν | 0 | a | a |

|   | а | ĸ | c |

|   |   |   |   |

|                                           | ls of Phase-Locked Loops                                                                 | 2  |  |  |  |  |  |  |

|-------------------------------------------|------------------------------------------------------------------------------------------|----|--|--|--|--|--|--|

| Applications of PLL IC's                  |                                                                                          |    |  |  |  |  |  |  |

| Overview of Exar's PLL Products           |                                                                                          |    |  |  |  |  |  |  |

| Choosing the                              | e Right PLL Circuit                                                                      | 6  |  |  |  |  |  |  |

| XR-\$200                                  | Multi-Function PLL System                                                                | 8  |  |  |  |  |  |  |

| XR-210                                    | FSK Modulator/Demodulator                                                                | 16 |  |  |  |  |  |  |

| XR-215                                    | Monolithic Phase-Locked Loop                                                             | 20 |  |  |  |  |  |  |

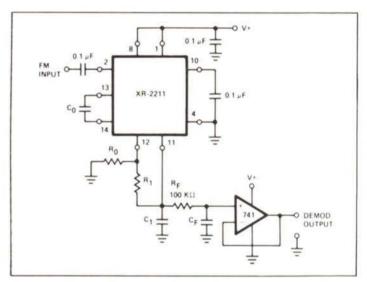

| XR-2211                                   | FSK Demodulator/Tone Decoder                                                             | 28 |  |  |  |  |  |  |

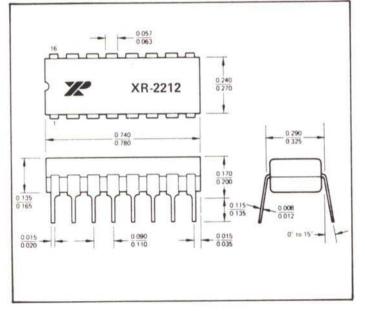

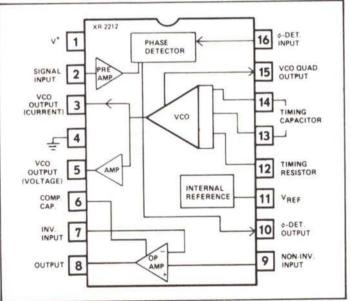

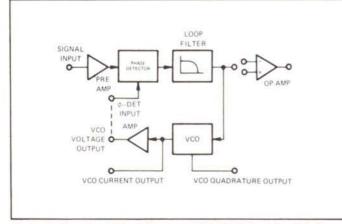

| XR-2212                                   | Precision Phase-Locked Loop                                                              | 34 |  |  |  |  |  |  |

| XR-567                                    | Monolithic Tone Decoder                                                                  | 40 |  |  |  |  |  |  |

| XR-L567                                   | Micropower Tone Decoder                                                                  | 48 |  |  |  |  |  |  |

| XR-2567                                   | Dual Monolithic Tone Decoder                                                             | 54 |  |  |  |  |  |  |

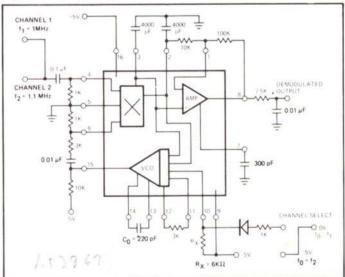

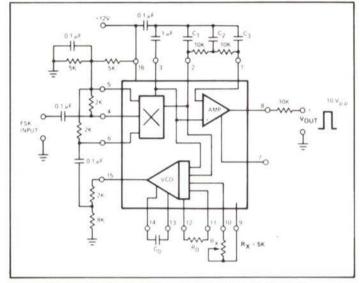

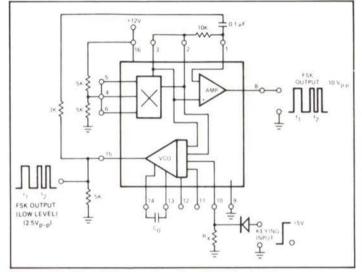

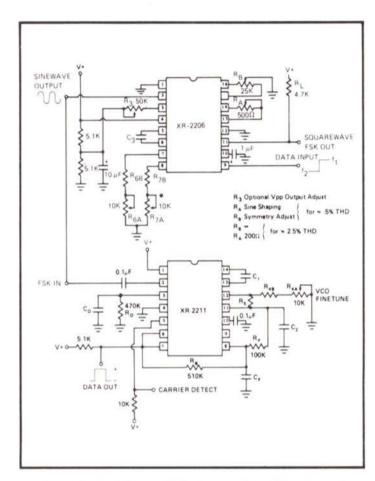

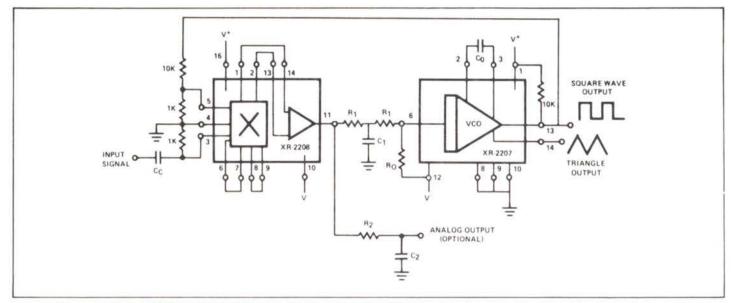

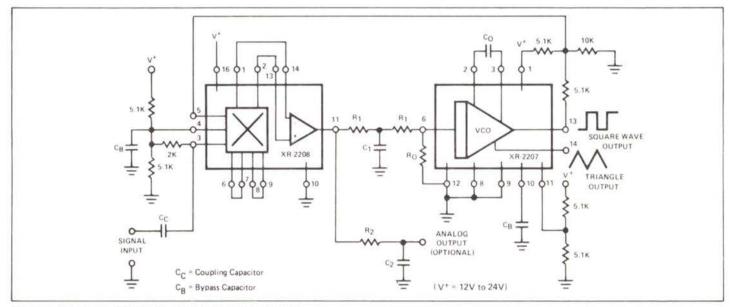

| AN-01                                     | Application Note<br>Stable FSK Modems Featuring the XR-2207, XR-2206, and XR-2211        | 62 |  |  |  |  |  |  |

| AN-06                                     | Application Note<br>Precision PLL System Using the XR-2207 and the XR-2208               | 67 |  |  |  |  |  |  |

| AN-12                                     | Application Note<br>Designing High-Frequency Phase-Locked Loop Carrier-Detector Circuits | 69 |  |  |  |  |  |  |

| AN-13                                     | Application Note<br>Frequency Selective AM Detection Using Monolithic Phase-Locked Loops | 72 |  |  |  |  |  |  |

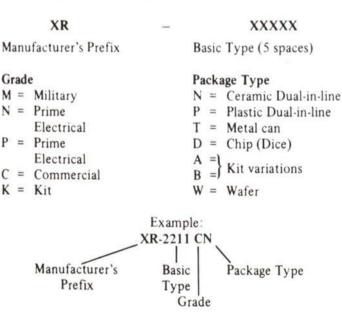

| Quality Ass                               | Quality Assurance Standards                                                              |    |  |  |  |  |  |  |

| Product Ordering Information              |                                                                                          |    |  |  |  |  |  |  |

| Monolithic Chips for Hybrid Assemblies    |                                                                                          |    |  |  |  |  |  |  |

| Additional Technical Literature from Exar |                                                                                          |    |  |  |  |  |  |  |

| Foreign Sales Offices and Representatives |                                                                                          |    |  |  |  |  |  |  |

| Authorized                                | Authorized Stocking Distributors                                                         |    |  |  |  |  |  |  |

| Authorized                                | Authorized Representatives                                                               |    |  |  |  |  |  |  |

# **Fundamentals of Phase-Locked Loops**

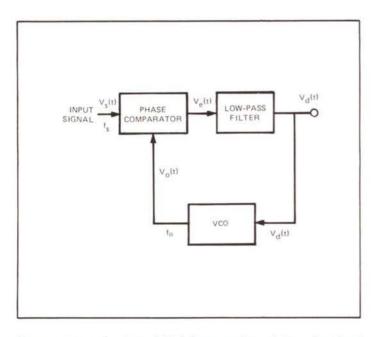

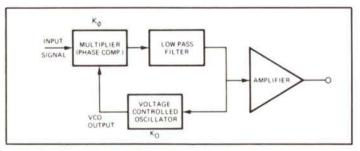

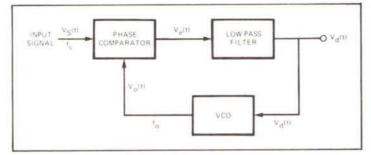

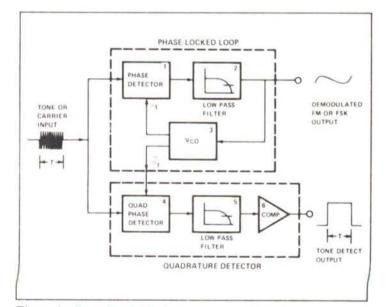

The phase locked loop provides frequency selective tuning and filtering without the need for coils or inductors. As shown in Figure 1, the PLL in its most basic form is a feedback system comprised of three basic functional blocks: a phase comparator, low-pass filter and voltage controlled oscillator (VCO).

The basic principle of operation of a PLL can briefly be explained as follows: With no input signal applied to the system, the error voltage  $V_d$  is equal to zero. The VCO operates at a set frequency,  $f_o$ , which is known as the free-running frequency. If an input signal is applied to the system, the phase comparator compares the phase and frequency of the input signal with the VCO frequency and generates an error voltage,  $V_e(t)$ , that is related to the phase and frequency difference between the two signals. This error voltage is then filtered and applied to the control terminal of the VCO. If the input frequency,  $f_s$ , is sufficiently close to  $f_o$ , the feedback nature of the PLL causes the VCO to synchronize, or lock, with the incoming signal. Once in lock, the VCO frequency is identical to the input signal, except for a finite phase difference.

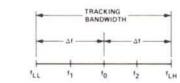

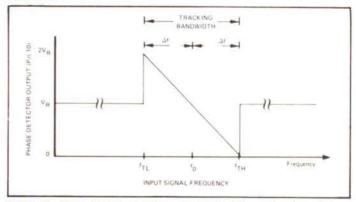

Two key parameters of a PLL system are its lock and capture ranges. They can be defined as follows:

Lock range: The range of frequencies in the vicinity of  $f_0$ , over which the PLL can maintain lock with an input signal. It is also known as the tracking or holding range. Lock range increases as the over-all gain of the PLL is increased.

**Capture range:** The band of frequencies in the vicinity of  $f_0$  where the PLL can establish or acquire lock with an input signal. It is also known as the acquisition range. It is always

smaller than the lock range and is related to the low-pass filter bandwidth. It decreases as the filter bandwidth is reduced.

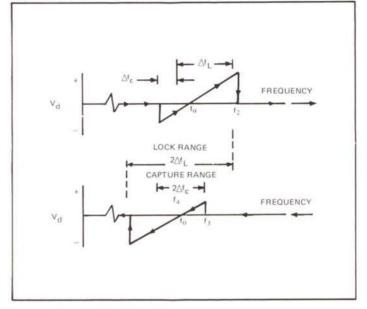

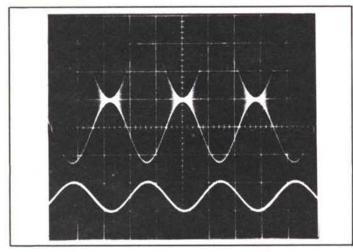

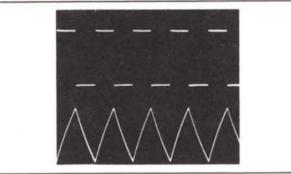

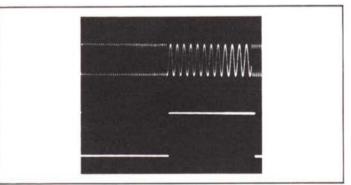

The lock and the capture ranges of a PLL can be illustrated with reference to Figure 2, which shows the typical frequencyto-voltage characteristics of a PLL. In the figure, the input is assumed to be swept slowly over a broad frequency range. The vertical scale corresponds to the loop error voltage.

In the upper part of Figure 2, the loop frequency is being gradually increased. The loop does not respond to the signal until it reaches a frequency  $f_1$ , corresponding to the lower edge of the capture range. Then, the loop suddenly locks on the input, causing a negative jump of the loop error voltage. Next,  $V_d$  varies with frequency with a slope equal to the reciprocal of the VCO voltage-to-frequency conversion gain, and goes through zero as  $f_s = f_0$ . The loop tracks the input until the input frequency reaches  $f_2$ , corresponding to the upper edge of the lock range. The PLL then loses lock, and the error voltage drops to zero.

If the input frequency is now swept slowly back, the cycle repeats itself as shown in the lower part of Figure 2. The loop recaptures the signal at  $f_3$  and traces it down to  $f_4$ . The frequency spread between  $(f_1, f_3)$  and  $(f_2, f_4)$  corresponds to the total capture and lock ranges of the system; that is,  $f_3 - f_1 =$  capture range and  $f_2 - f_4 =$  lock range. The PLL responds only to those input signals sufficiently close to the VCO frequency,  $f_0$ , to fall within the "lock" or "capture" range of the system. Its performance characteristics, therefore, offer a high degree of frequency selectivity, with the selectivity characteristics centered about  $f_0$ .

Figure 1. The basic phase locked loop consists of three functional blocks: a phase comparator, a low pass filter and a voltage-controlled oscillator.

Figure 2. Typical PLL frequency-to-voltage transfer characteristics are shown for increasing (upper diagram) and decreasing (lower diagram) input frequency.

# **Applications of PLL IC's**

The basic concept of the phase locked loop (PLL) has been around since the early 1930's and has been used for a variety of applications in instrumentation and space telemetry. However, before the advent of monolithic integration, cost and complexity considerations limited its use to precision measurements requiring very narrow bandwidths. In the past few years, the advantages of monolithic integration have changed the phase locked loop from a specialized design technique to a general-purpose building block. Therefore, what is "new" at this point is not the concept of the PLL, but its availability in a low-cost self contained monolithic IC package.

In many ways, this is similar to the case of the monolithic operational amplifier, which, until less than a decade ago, was an expensive building block. Today, with the advent of monolithic technology, it has become a basic building block in nearly every system design. The monolithic phase locked loop also offers a similar potential. In fact, many of the applications of the PLL outlined in this article become economically feasible only because the PLL is now available as a low-cost IC building block.

Today, over a dozen different integrated PLL products are available from a number of IC manufacturers. Some of these are designed as "general-purpose" circuits, suitable for a multitude of uses; others are intended or optimized for special applications such as tone detection, stereo decoding and frequency synthesis. This article is intended as a brief survey of the expanding field of monolithic phase locked loops. Its purpose is to familiarize the reader with their individual characteristics, capabilities and applications.

#### Applications for PLLs Abound

As a versatile building block, the PLL covers a wide range of applications. Some of the more important are the following:

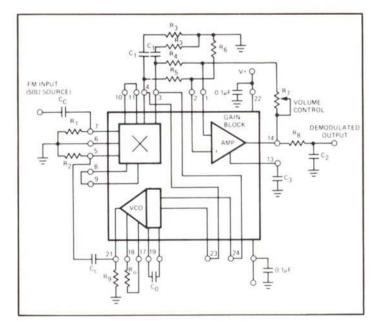

FM demodulation: In this application, the PLL is locked on the input FM signal, and the loop-error voltage,  $V_d(t)$  in Figure 1 (see Box), which keeps the VCO in lock with the

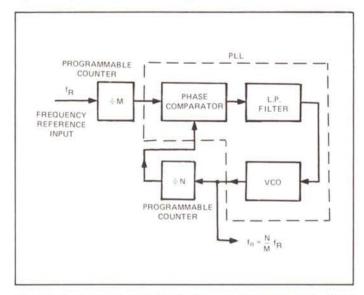

Figure 3. A frequency multiplier/divider can be constructed using a phase locked loop.

input signal, represents the demodulated output. Since the system responds only to input signals within the capture range of the PLL, it also provides a high degree of frequency selectivity. In most applications, the quality of the demodulated output (i.e., its linearity and signal/noise ratio) obtained from a PLL is superior to that of a conventional discriminator.

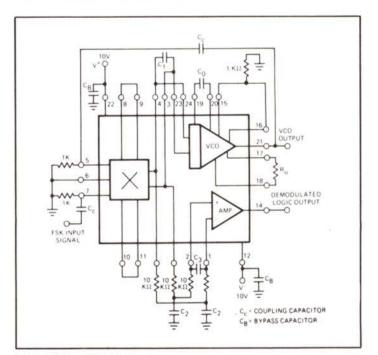

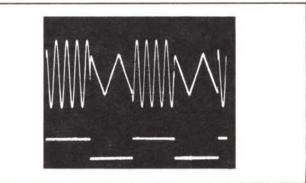

**FSK demodulation:** Frequency-shift keyed (FSK) signals are commonly used to transmit digital information over telephone lines. In this type of modulation, the carrier signal is shifted between two discrete frequencies to encode the binary data. When the PLL is locked on the input signal, tracking the shifts in the input frequency, the error voltage in the loop,  $V_d(t)$ , converts the frequency shifts back to binary logic pulses.

Signal conditioning: When the PLL is locked on a noisy input signal, the VCO output duplicates the frequency of the desired input but greatly attenuates the noise, undesired sidebands and interference present at the input. It is also a tracking filter since it can track a slowly varying input frequency.

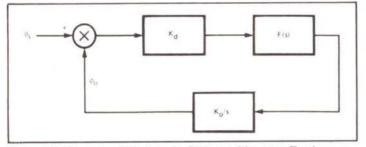

Frequency synthesis: The PLL can be used to generate new frequencies from a stable reference source by either frequency multiplication and division, or by frequency translation. Figure 3 shows a typical frequency multiplication and division circuit, using a PLL and two programmable counters. In this application, one of the counters is inserted between the VCO and phase comparator and effectively divides the VCO frequency by the counter's modulus N. When the system is in lock, the VCO output is related to the reference frequency,  $f_R$ , by the counter moduli M and N as:

$$f_0 = (\frac{N}{M}) f_R$$

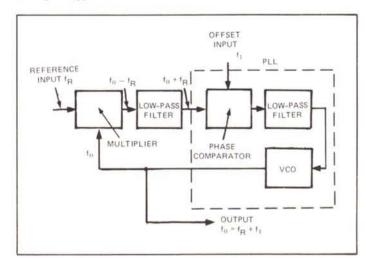

By adding a multiplier and an additional low-pass filter to a PLL (Figure 4), one can form a frequency translation loop. In this application, the VCO output is shifted from the reference frequency,  $f_R$ , by an amount equal to the offset frequency,  $f_1$ , i.e.,  $f_0 = (f_R + f_1)$ .

Figure 4. Frequency translation can be accomplished with a phase locked loop by adding a multiplier and an additional low-pass filter to the basic PLL.

Data synchronization: The PLL can be used to extract synchronization from a composite signal, or can be used to synchronize two data streams or system clocks to the same frequency reference. Such applications are useful in PCM data transmission, regenerative repeaters, CRT scanning and or drum memory read-write synchronization.

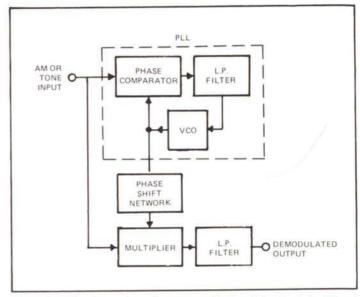

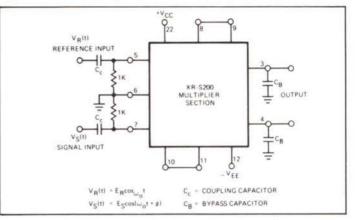

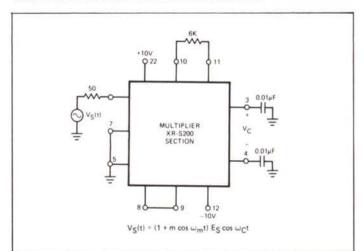

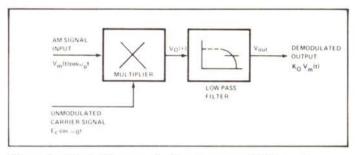

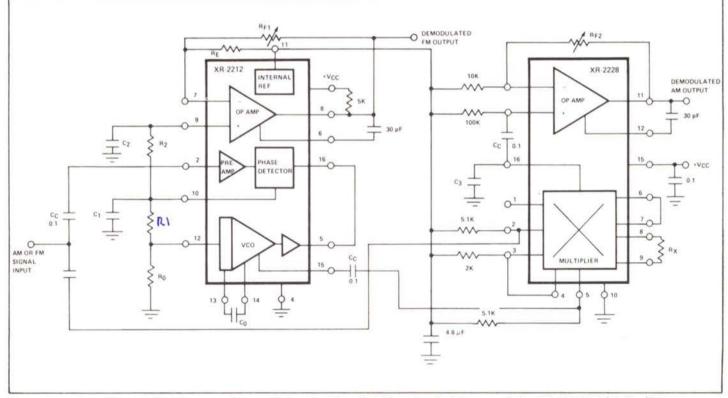

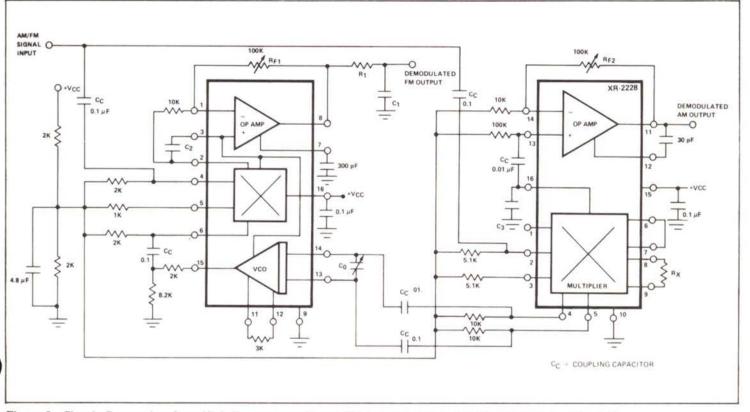

AM detection: The PLL can be converted to a synchronous AM detector with the addition of a non-critical phase-shift network, an analog multiplier and a low-pass filter. The system block diagram for this application is shown in Figure 5.

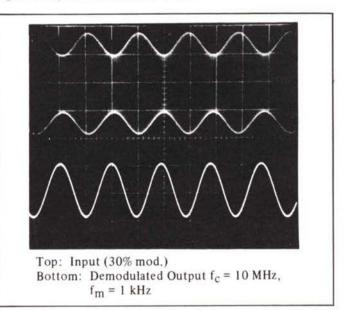

In this application, as the PLL tracks the carrier of the input signal, the VCO regenerates the unmodulated carrier and feeds it to the reference input of the multiplier section. In this manner, the system functions as a synchronous demodulator with the filtered output of the multiplier representing the demodulated audio information.

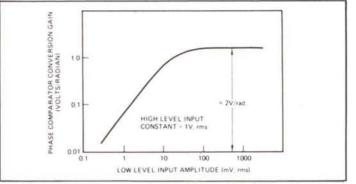

Tone detection: In this application, the PLL is again connected as shown in Figure 5. When a signal tone is present at the input, within a frequency band corresponding to the capture range of the PLL, the output dc voltage is shifted from its tone-absent level. This shift is easily converted to a logic signal by adding a threshold detector with logic-compatible output levels.

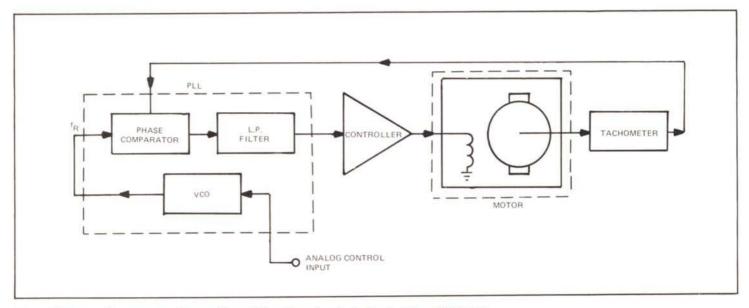

Motor speed control: Many electromechanical systems, such as magnetic tape drives and disc or drum head drivers, require precise speed control. This can be achieved using a PLL system, as shown in Figure 6. The VCO section of the monolithic PLL is separated from the phase-comparator and used to generate a voltage controlled reference frequency,  $f_R$ . The motor shaft and the tachometer output provide the second signal, frequency  $f_M$ , which is compared to the reference frequency. The controller is a power amplifier which drives the speed-control

Figure 5. AM and tone detection are possible by adding three functional blocks to the basic phase locked loop.

windings of the motor. Thus, the motor and tachometer combination essentially functions as a VCO which is phase locked to the voltage controlled reference frequency, f<sub>R</sub>.

Stereo decoding: In commercial FM broadcasting, suppressed carrier AM modulation is used to superimpose the stereo information on the FM signal. To demodulate the complex stereo signal, a low-level pilot tone is transmitted at 19 kHz (1/2 of actual carrier frequency). The PLL can be used to lock onto this pilot tone, and regenerate a coherent 38 kHz carrier which is then used to demodulate the complete stereo signal. A number of highly specialized monolithic circuits have been developed for this application. A typical example of monolithic stereo decoder circuits using the PLL principle is the XR-1310 stereo demodulator IC.

Figure 6. Very precise motor speed control is possible with a phase locked loop system of this type.

# **Overview of Exar's PLL Products**

Exar offers the widest selection of monolithic phase-locked loop IC products in the industry. The purpose of this section is to familiarize the user with the key features and the characteristics of Exar's entire line of PLL products. Table 1 gives a comparative listing of the key features and characteristics of Exar's broad line of PLL products.

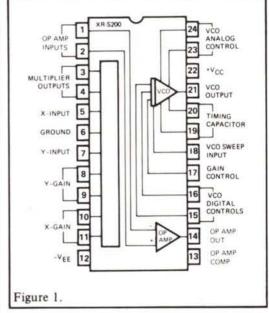

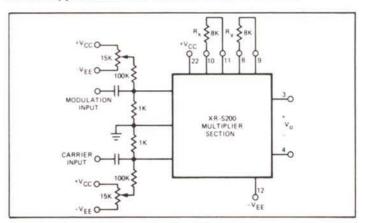

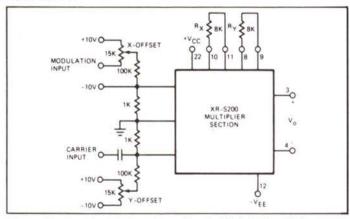

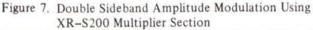

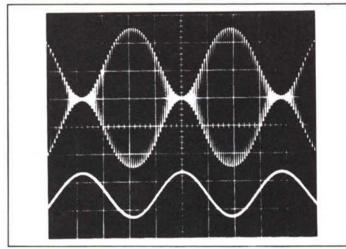

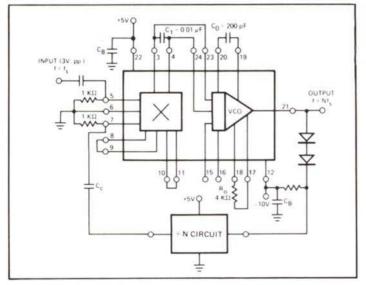

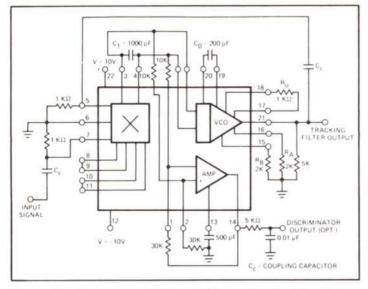

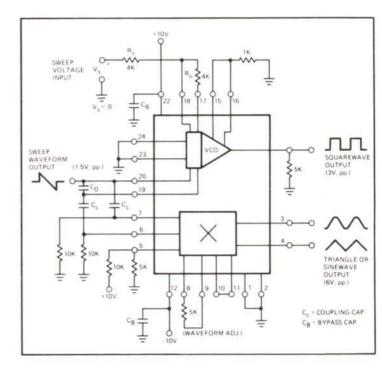

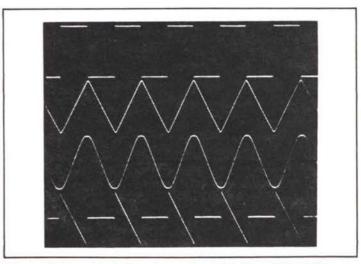

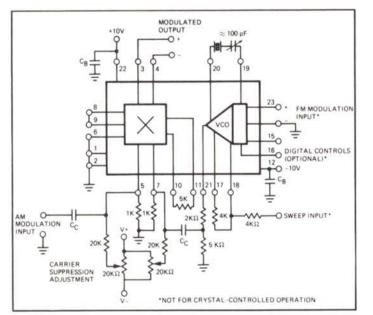

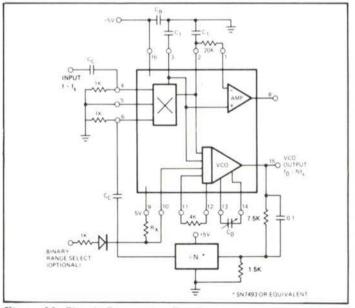

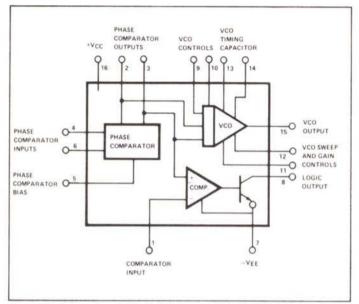

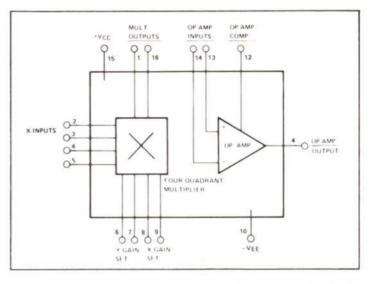

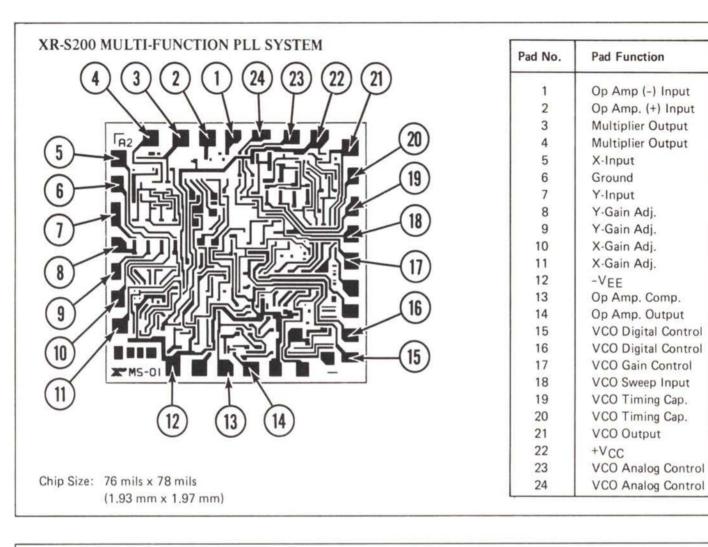

**XR-S200** is a multi-function PLL containing a four-quadrant analog multiplier, a high-frequency VCO and an operational amplifier, and is housed in a 24-pin package. Each of the functional blocks and their control inputs are independent of each other. In other words, they can be externally connected in any order. Thus, it is essentially a custom, or do-it-yourself, PLL. The user determines the function and performance characteristics by his choice of external connections and components.

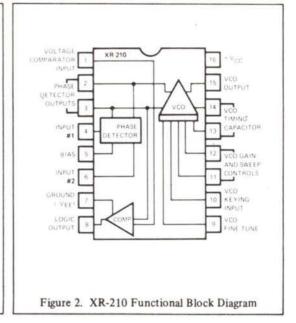

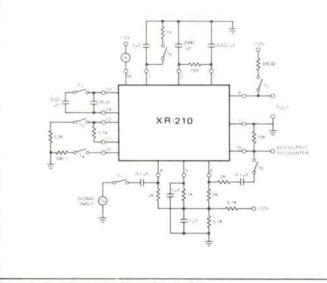

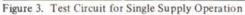

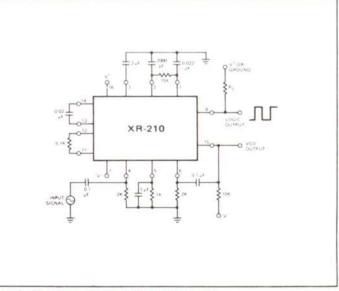

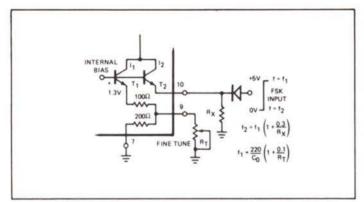

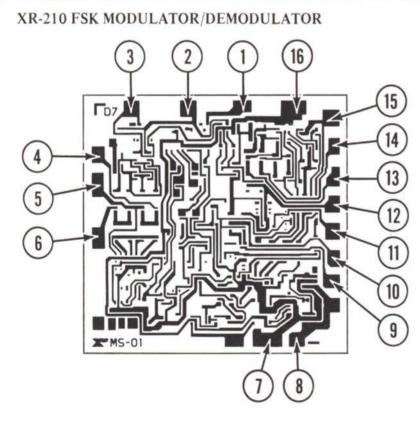

**XR-210** was designed for FSK modulation/demodulation applications. In addition to the basic PLL, it contains a voltage comparator and a RS232-C compatible output logic driver. The VCO section can be used for FSK modulation and has independent mark/space adjustments.

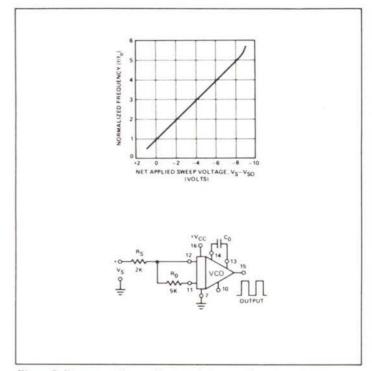

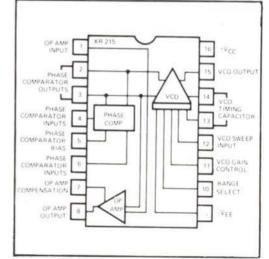

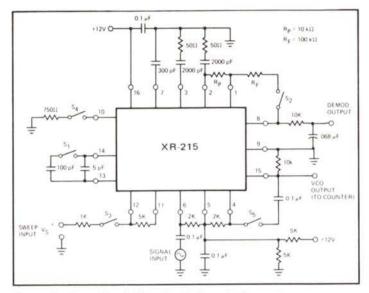

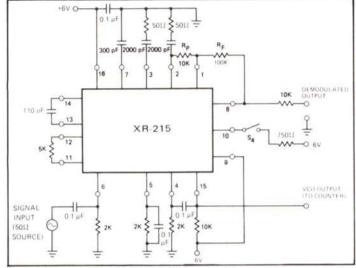

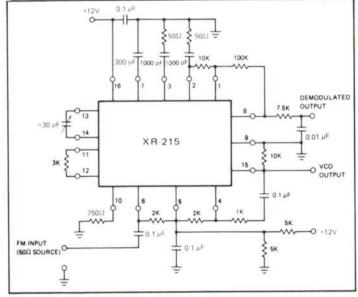

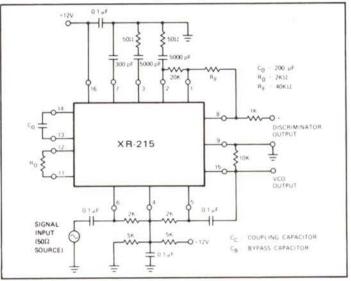

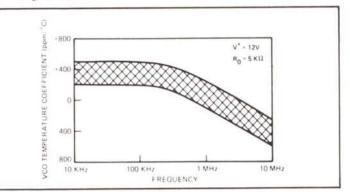

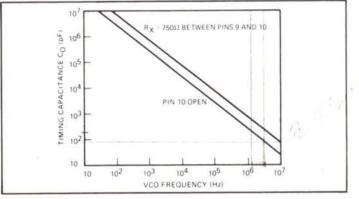

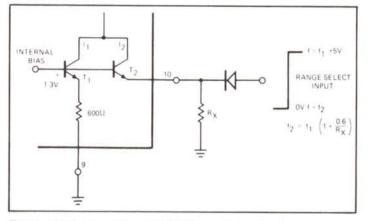

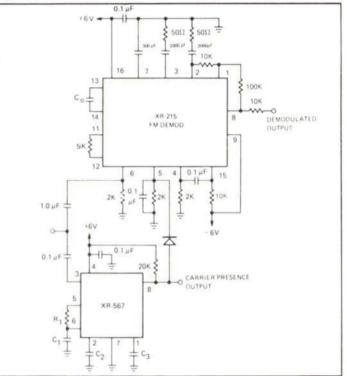

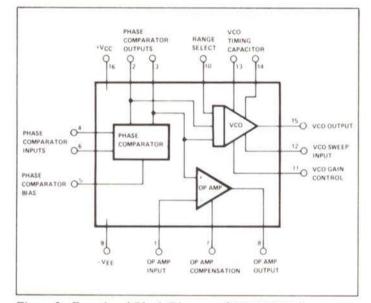

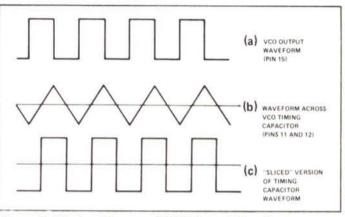

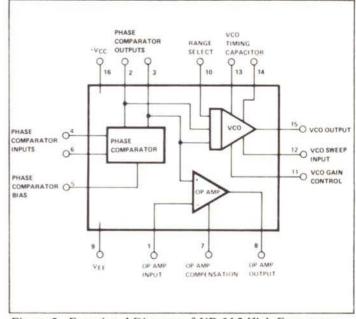

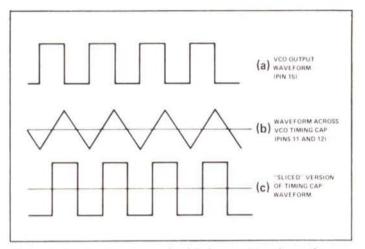

**XR-215** is a general-purpose PLL circuit particularly suited for FM demodulation, frequency synthesis, and tracking filter. The high-gain amplifier section can be used as an active filter, or can function as an audio preamplifier for FM detection. The VCO section has sweep and gain control options. A single PLL circuit can be time-multiplexed between two input channels by applying a binary input to its range-select control. The key feature of XR-215 is its high frequency capability (up to 35 MHz).

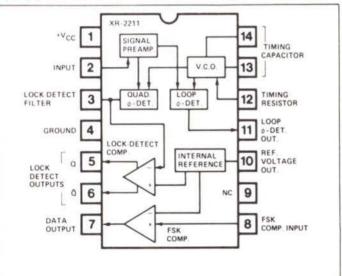

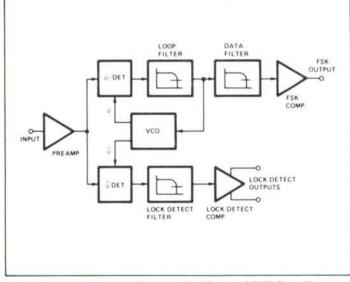

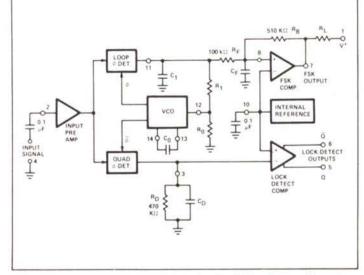

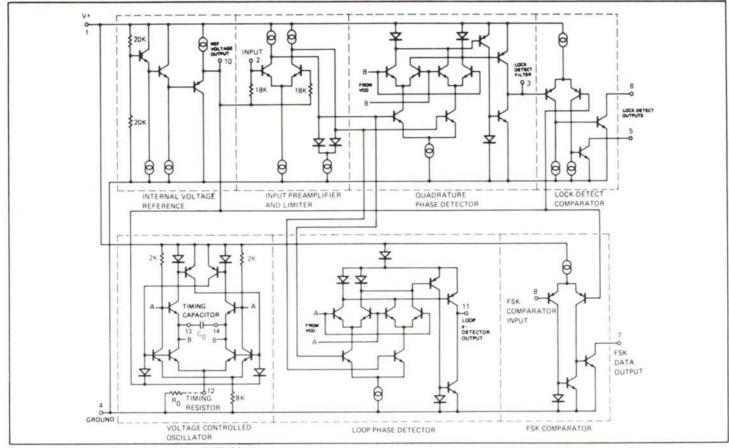

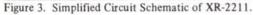

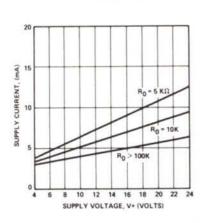

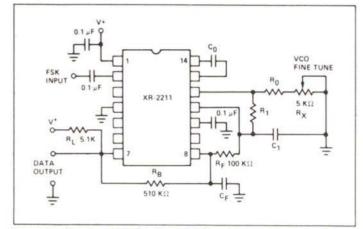

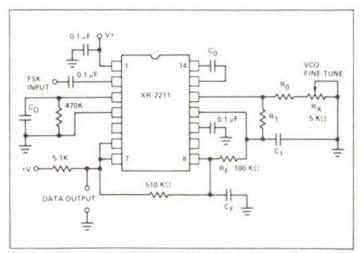

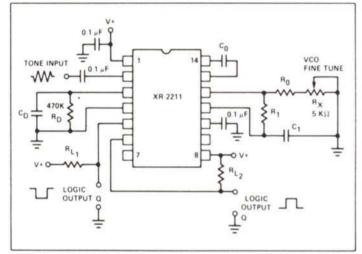

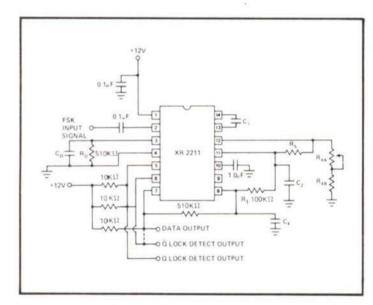

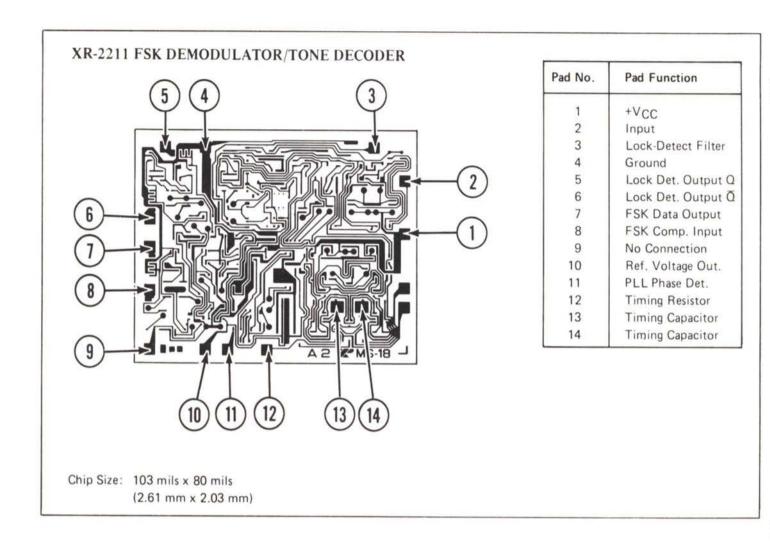

**XR-2211** is an ultra-stable PLL system optimized for FSK MODEM design. It offers 20 ppm/°C VCO stability and an on-chip quadrature detector for time or carrier-detect applications. Its tracking bandwidth can be controlled by choice of two external resistors.

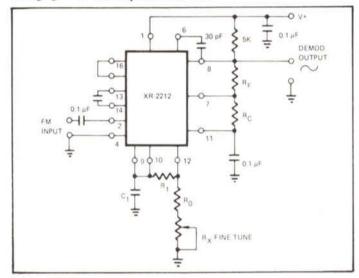

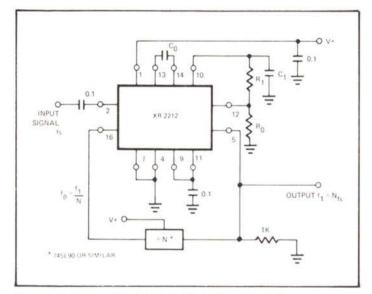

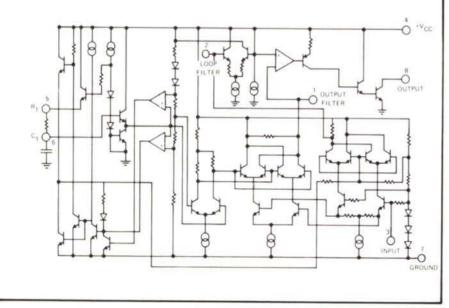

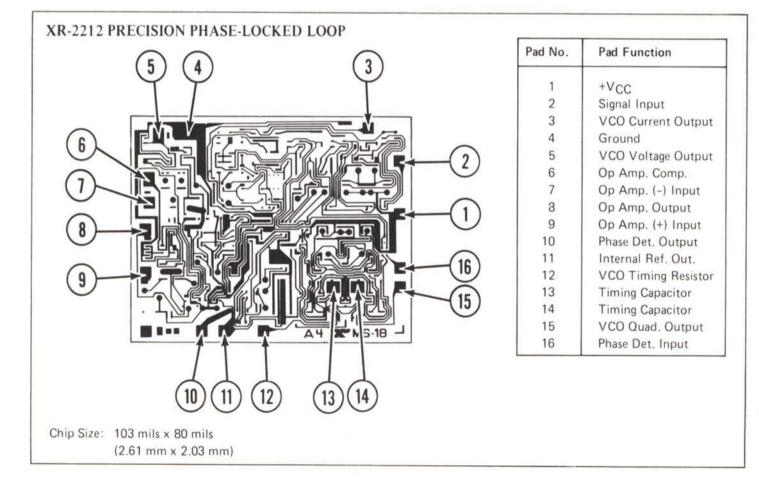

**XR-2212** is a versatile, precision PLL circuit with 20 ppm/°C oscillator stability. It is ideally suited for linear FM detection or frequency synthesis. The VCO section of the circuit is not internally connected to the phase-detector; thus, it can interface with an external TTL or MOS frequency divider for frequency synthesis applications.

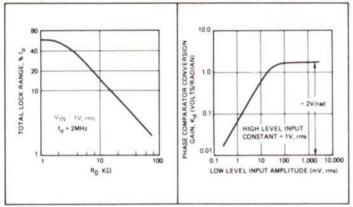

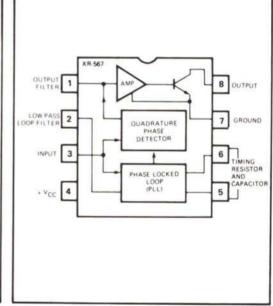

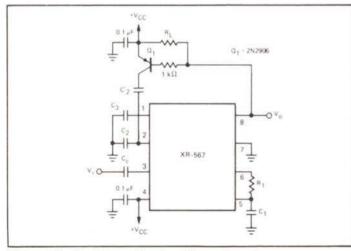

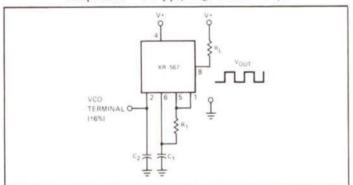

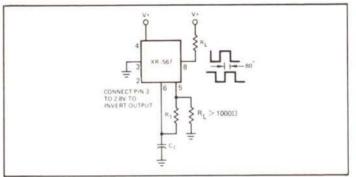

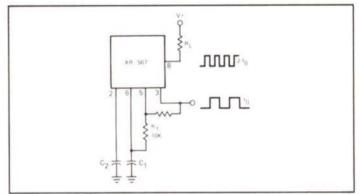

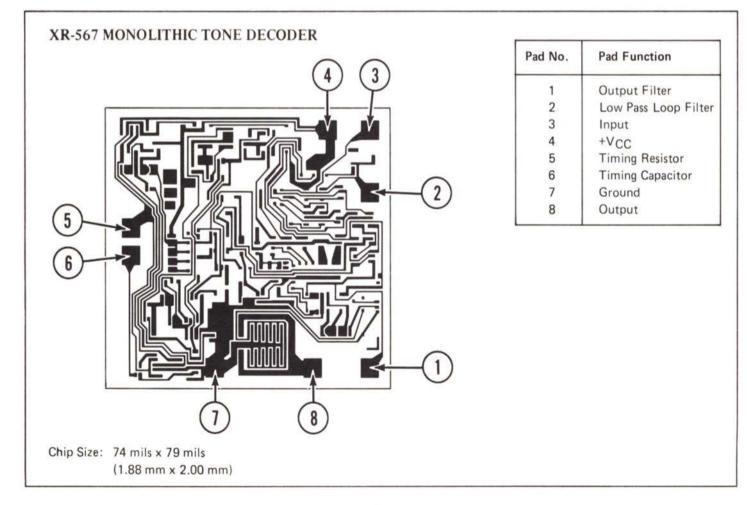

**XR-567** monolithic tone-decoder contains an internal currentcontrolled oscillator (CCO) and two separate phase-detectors driven from the same oscillator. The quadrature phase-detector, along with the buffer amplifier, is used to generate a binary output pulse if a signal tone at the input is within the passband of the system. Its detection bandwidth (capture range) and response time are controlled by external filter capacitors. It has high-current (100 mA) logic driver output.

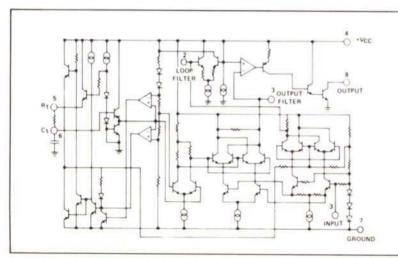

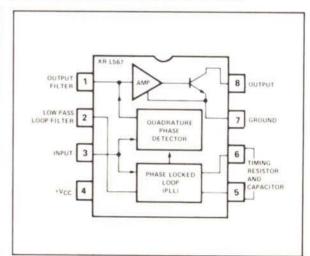

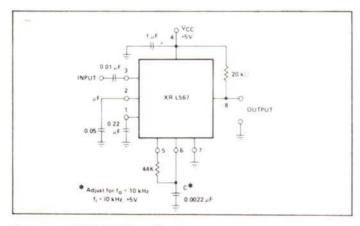

**XR-L567** monolithic tone decoder is the low-power equivalent of the XR-567 tone decoder IC. It is specifically intended for use in battery-powered or portable equipment where the low stand-by power dissipation is essential. The XR-L567 offers approximately 1/10th the power dissipation of the conventional 567-type tone decoder, without sacrificing its key features such as the oscillator stability, frequency selectivity and detection threshold. At 5 volt operation, typical quiescent power dissipation is less than 4 mW. It operates over a wide frequency band of 0.01 Hz to 50 kHz and contains a logic compatible output which can sink up to 10 milliamps of load current.

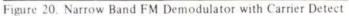

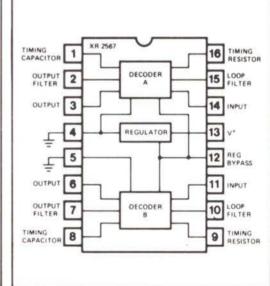

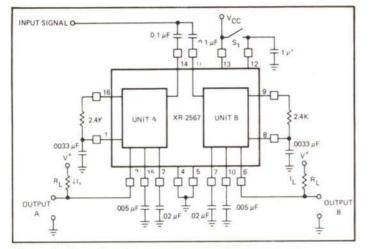

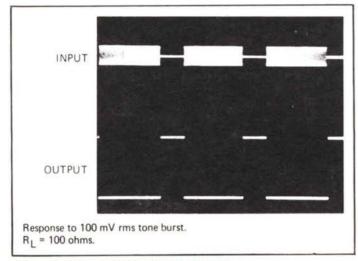

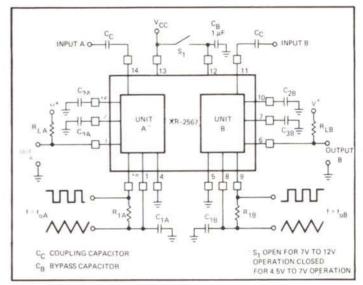

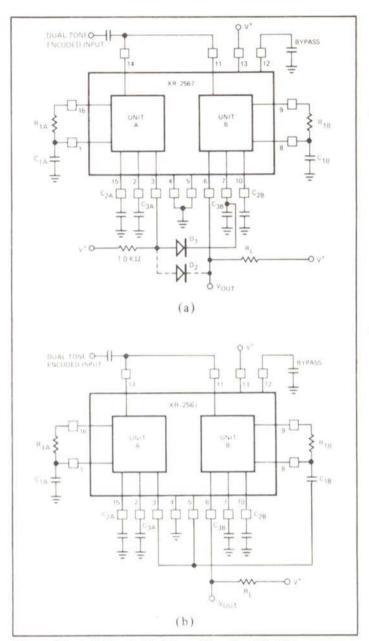

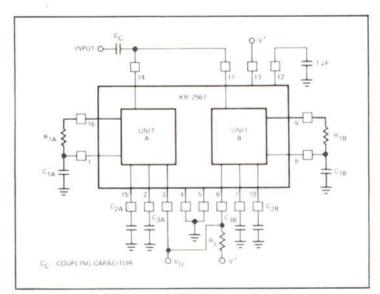

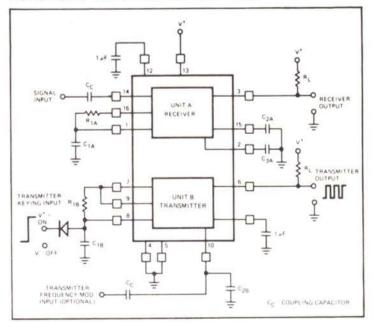

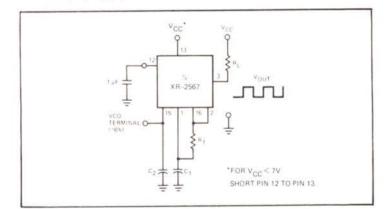

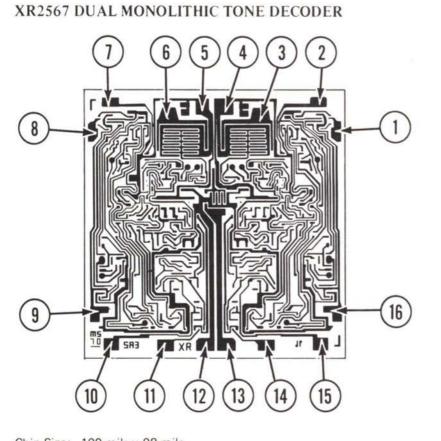

**XR-2567** dual tone-decoder system contains an equivalent of two independent 567 decoders on the same chip. It is particularly well suited for decoding multiple-tone inputs, such as those used in telephone dialing systems. Its operating voltage range is wider than that of the 567, and can switch two simultaneous 100 mA loads at the outputs. If only one of the two decoders is used, the remaining one can be deactivated to minimize power dissipation.

|                        |            |                           | High               | VCC                      | ) Stability            |                                                                             |

|------------------------|------------|---------------------------|--------------------|--------------------------|------------------------|-----------------------------------------------------------------------------|

| Product<br>Designation | Package    | Operating<br>Supply Range | Frequency<br>Limit | Power<br>Supply<br>(%/V) | Temp.<br>(ppm/°C)      | Primary Applications                                                        |

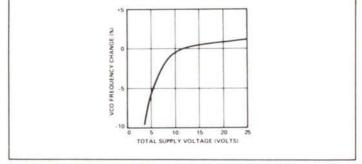

| XR-S200                | 24 Pin DIP | 6V to 30V<br>±3V to ±15V  | 30 MHz             | 0.08 (typ)<br>0.5 (max)  | 300 (typ)<br>650 (max) | Multi-function building block for<br>FM/FSK detection, frequency synthesis  |

| XR-210                 | 16 Pin DIP | 5V to 26V                 | 20 MHz             | 0.05 (typ)<br>0.5 (max)  | 200 (typ)<br>550 (max) | FSK modem, frequency synthesis, data synchronization                        |

| XR-215                 | 16 Pin DIP | 5V to 26V                 | 35 MHz             | 0.1 (typ)<br>0.5 (max)   | 250 (typ)<br>600 (max) | General purpose PLL. FM demodulation tracking filter, frequency synthesis   |

| XR-2211                | 16 Pin DIP | 4.5V to 20V               | 300 kHz            | 0.05 (typ)<br>0.5 (max)  | ±20 (typ)<br>±50 (max) | FSK demodulation, tone decoding, carrier detection                          |

| XR-2212                | 16 Pin DIP | 4.5V to 20V               | 300 k Hz           | 0.05 (typ)<br>0.5 (max)  | ±20 (typ)<br>±50 (max) | Frequency synthesis, FM detection,<br>data synchronization, tracking filter |

| XR-567                 | 8 Pin DIP  | 4.75V to 9V               | 500 kHz            | 0.5 (typ)<br>1 (max)     | ±140 (typ)             | Tone detection                                                              |

| XR-L567                | 8 Pin DIP  | 4.75V to 9V               | 50 kHz             | 0.5 (typ)<br>2 (max)     | -150 ppm<br>(typ)      | Tone detection low-power equivalent<br>of XR-567                            |

| XR-2567                | 16 Pin DIP | 4.75V to 15V              | 600 k Hz           | 0.05 (typ)<br>0.2 (max)  | ±100 (typ)             | Dual tone decoder (Dual 567 equivalent)                                     |

Table 1. A Summary of Exar's PLL Circuits

# **Choosing the Right PLL Circuit**

At the onset of his design, the user of monolithic PLL products is faced with the key question of choosing the phase-locked loop IC best suited to his application. The broad line of PLL products offered by Exar cover a wide range of applications. It is often difficult to determine at a glance the best circuit for a given application. The purpose of this section is to review some of the key performance requirements, from an applications point of view, and help answer the question, "What is the best PLL product for the job?"

Table 2 gives a brief listing of some of the major classes of PLL applications, and lists the recommended circuits for each. A further discussion of the key performance parameters associated with each application are also listed below.

FM demodulation: Essentially all the PLL circuits listed in Table 1 can be used for FM demodulation. However, it is often possible to narrow the choice down to 2 or 3 circuits, based on the particular performance criteria. In general, there are three key performance parameters which should be examined:

- □ Quality of demodulated output: This is normally measured in terms of the output level, distortion, and signal/noise ratio for a given FM deviation.

- □ VCO frequency range and frequency stability: For reliable operation, VCO upper frequency limit (see Table 1) should be at least 20% above the FM carrier frequency. VCO frequency stability is important, especially if a narrow-band filter is used in front of the PLL, or multiple input channels are present. If the VCO exhibits excessive drift, the PLL can drift out of the input signal band as the ambient temperature varies.

- □ Detection threshold: This parameter determines minimum signal level necessary for the PLL to lock and demodulate an FM signal of given deviation.

In most FM demodulation applications, it is also desirable to control the amplitude of the demodulated output. This feature is provided in some of the PLL circuits (such as the XR-215 and the XR-2212) by means of a variable-gain amplifier contained on the chip.

For low-frequency FM detection (below 300 kHz carrier frequency) the XR-2212 is recommended because of its versatility and temperature stability. For FM demodulation at frequencies above 300 kHz, the XR-2215 offers the best performance because of its high frequency capability.

FSK decoding: Frequency-shift keying used in digital communications is very similar to analog FM modulation. Therefore, any PLL IC can be used for FSK decoding, provided that its input sensitivity and the tracking range are sufficient for a given FSK signal deviation. Some of the basic requirements and desirable features for a PLL used in FSK decoding are:

- □ Center frequency stability.

- □ Logic compatible output.

- □ Control of VCO conversion gain.

Center frequency stability is essential to insure that the VCO frequency range stays within the signal band over the operating temperature range. A logic compatible output is desirable to avoid the need for an external voltage comparator (slicer) to square the output pulses. It is particularly convenient if the output conforms to RS-232C standard, thereby eliminating the need for a separate line-driver circuit. Control of the VCO's conversion gain allows the circuit to be used for both large deviation FSK signals (such as 1200 baud operation) as well as for small deviation (75 baud) FSK signals.

For FSK decoding at low frequencies (i.e. below 300 kHz) the XR-2211 is by far the optimum circuit to use because of its frequency stability and carrier-detect capability. For FSK detection at higher frequencies (up to 10 MHz) the XR-210 is the recommended circuit.

Frequency synthesis: This application requires a PLL circuit with the loop opened between the VCO output and the phase comparator input, so that an external frequency divider can be inserted into the feedback loop of the PLL. This requirement is satisfied by XR-S200, XR-210, XR-215 and the XR-2212 PLL circuits.

For frequency synthesis at low frequencies (i.e. with maximum output frequency less than 300 kHz) the XR-2212 is by far the best suited circuit since it has the best VCO stability and interfaces easily with all logic families. For operation above 300 kHz, either the XR-210 or the XR-215 PLL IC's can be used for frequency synthesis; however the XR-215 offers the highest frequency capability.

Signal conditioning: Most signal conditioning applications require very narrow-band operation of the PLL. This in turn may require the use of active filters within the loop (between the phase detector and the VCO). The PLL circuits which allow active filters to be inserted into the loop are the XR-S200 and the XR-2212. Both of these circuits already contain an op. amp. on the chip for active filtering. For low frequencies (i.e. below 300 kHz) the XR-2212 is the best suited circuit because of its adjustable tracking bandwidth and excellent frequency stability. For higher frequencies the XR-S200 is the recommended circuit.

**Tone decoding:** The PLL circuits especially designed for this application are the XR-567, the XR-L567, the XR-2567 and the XR-2211. The XR-2211 offers the highest frequency stability, and independent control of system bandwidth and response time, among the three circuits. The XR-567 has a relatively high input threshold ( $\approx 20 \text{ mV}$ , rms) and may require input preamplification; however it requires fewer external components than the XR-2211. The XR-2567, which contains two independent 567-type tone decoders on the same chip may be more economical to use in multiple-tone detection systems.

**Motor speed control:** In most speed-control applications, a tachometer connected to the motor shaft is used as the VCO in the loop and the actual VCO on the monolithic chip is either not used or used to generate a reference frequency (see Figure 6). Thus, a PLL system which can be broken between the low-pass filter and the VCO is needed. The PLL IC most suited to this application is the XR-2212 because of its wide tracking range.

Low-power operation: In applications requiring batterypowered operation, low stand-by power dissipation is essential, to assure long battery life. The XR-L567 micropower tone decoder PLL is specifically designed for such applications. Its stand-by power dissipation is less than 5 mW at 5 volt operation, and is suitable for operation up to 50 kHz. This power dissipation is approximately 1/10th of the power consumption of the conventional 567-type tone decoder.

AM detection: This application requires an additional analog multiplier section to be added to the basic PLL (see Figure 3). The XR-2208 Operational Multiplier IC which contains a four-quadrant multiplier and an op. amp. on the same chip is ideally suited for this function. It can be used in conjunction with either the XR-215 or the XR-2212 PLL circuits to perform this function.

| MAJOR                                 | PART NUMBER  |                      |                      |              |              |        |         |              |  |

|---------------------------------------|--------------|----------------------|----------------------|--------------|--------------|--------|---------|--------------|--|

| APPLICATION                           | XR-S200      | XR-210               | XR-215               | XR-2211      | XR-2212      | XR-567 | XR-L567 | XR-2567      |  |

| FM DEMODULATION<br>HIGH FREQUENCY     | <b>v</b>     | $\checkmark$         | $\checkmark$         |              |              |        |         |              |  |

| LOW FREQUENCY                         |              |                      | <ul> <li></li> </ul> |              | $\checkmark$ |        |         |              |  |

| FREQUENCY SYNTHESIS<br>HIGH FREQUENCY | $\checkmark$ | ~                    | ~                    |              |              |        |         |              |  |

| LOW FREQUENCY                         |              | $\checkmark$         | $\checkmark$         |              | $\checkmark$ |        |         |              |  |

| FSK DEMODULATION                      |              | <ul> <li></li> </ul> |                      | ~            |              |        |         |              |  |

| SIGNAL CONDITIONING                   | ~            |                      |                      |              | ~            |        |         |              |  |

| TONE DETECTION                        |              |                      |                      | $\checkmark$ |              | ~      | V       | $\checkmark$ |  |

| MOTOR SPEED CONTROL                   | ~            |                      |                      |              | $\checkmark$ |        |         |              |  |

| DATA SYNCHRONIZATION                  |              |                      | $\checkmark$         |              | $\checkmark$ |        |         |              |  |

| LOW POWER OPERATION                   |              |                      |                      |              |              |        | V       |              |  |

Table 2 Major Applications for Exar's PLL Circuits

# XR-S200

# **Multi-Function PLL System**

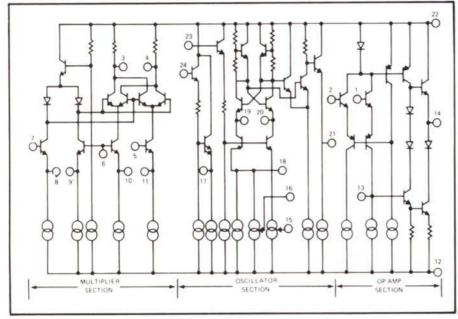

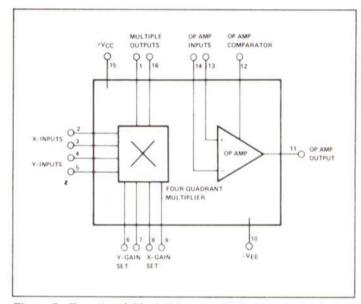

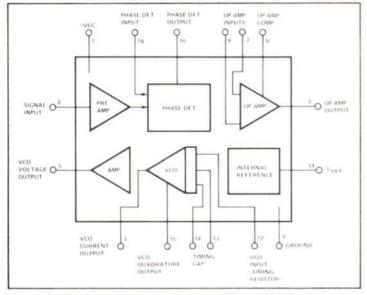

The XR-S200 integrated circuit is a highly versatile, multipurpose circuit that contains all of the essential functions of most communication system designs on a single monolithic substrate. The functions contained in the XR-S200 include:

(1) a four quadrant analog multiplier, (2) a high frequency voltage controlled oscillator (VCO) and

(3) a high performance operational amplifier.

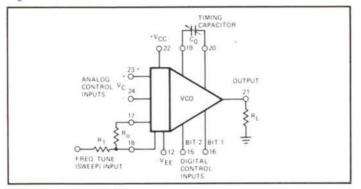

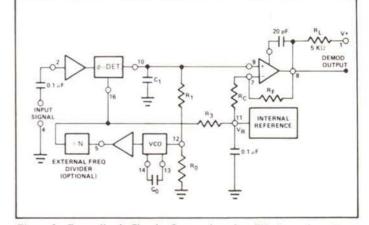

The three functions (Figure 1) can be used independently, or directly interconnected in any order to perform a large number of complex circuit functions. from phase-locked loops to the generation of complex waveforms. The XR-S200 can accomodate both analog and digital signals, over a frequency range of 0.1 Hz to 30 MHz, and operate with a wide choice of power supplies extending from  $\pm 3$  volts to  $\pm 30$  volts.

# **TYPICAL APPLICATIONS OF THE XR-S200**

#### Phase-locked loops

- FM demodulation

- Narrow and wideband FM

Commercial FM-IF

TV sound and SCA detection

- FSK detection (MODEM)

- PSK demodulation

- Signal conditioning

- Tracking filters

- Frequency synthesis

- Telemetry coding/decoding

- AM detection

- Quadrature detectors

Synchronous detectors

- Linear sweep & AM generation

- Crystal controlled

Suppressed carrier

- Double sideband

- Tone generation/detection

- Waveform generation

- Single/square/triangle/sawtooth

- Analog multiplication

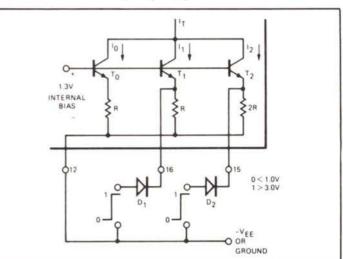

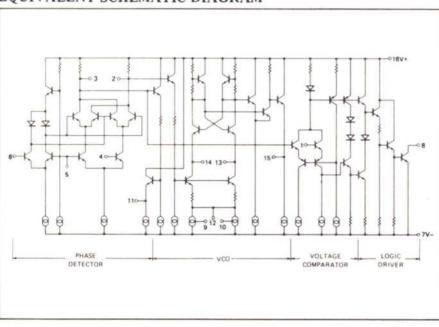

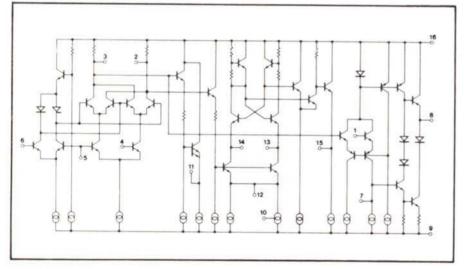

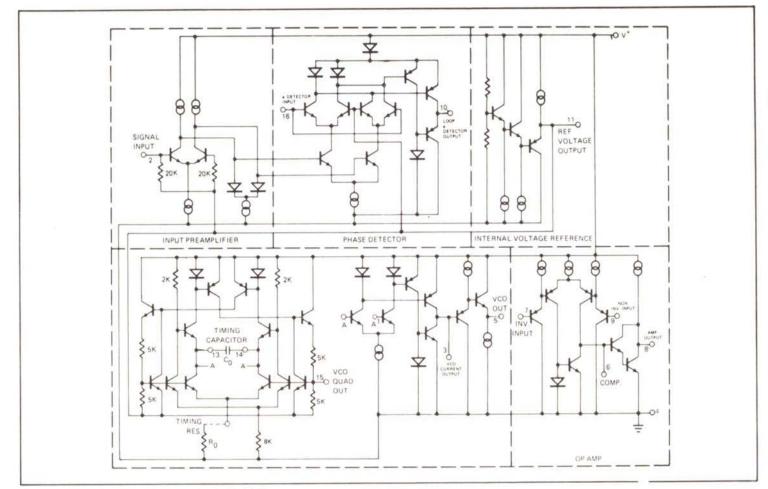

# EQUIVALENT SCHEMATIC DIAGRAM

# ABSOLUTE MAXIMUM RATINGS

| Power Supply                       | 30 volts                          |

|------------------------------------|-----------------------------------|

| Power Dissipation                  | 900 mW                            |

| Derate above +25°C                 | 5 mW/°C                           |

| Temperature                        | 0                                 |

| Operating                          | $-55^{\circ}C$ to $+125^{\circ}C$ |

| Storage                            | $-65^{\circ}C$ to $+150^{\circ}C$ |

| Input Signal Level, V <sub>S</sub> | 6 V,p-p                           |

## **AVAILABLE TYPE**

| Part Number | Package | Operating Temperature            |

|-------------|---------|----------------------------------|

| XR-S200     | Ceramic | $0^{\circ}$ C to $+75^{\circ}$ C |

### FUNCTIONAL BLOCK DIAGRAM

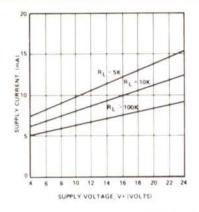

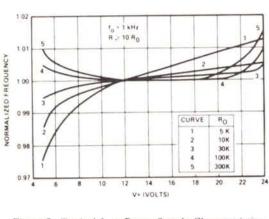

# **ELECTRICAL SPECIFICATIONS** $(T = 25^{\circ}C, V_{SUPPLY} = \pm 10V)$

| CUARA CTERICTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LIMITS                   |               |                 |                 | CONDITIONS                                     |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------|-----------------|-----------------|------------------------------------------------|--|

| CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MIN.                     | TYP.          | MAX.            | UNITS           | CONDITIONS                                     |  |

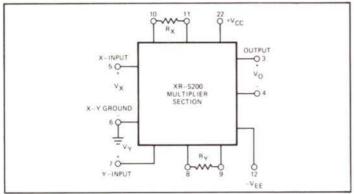

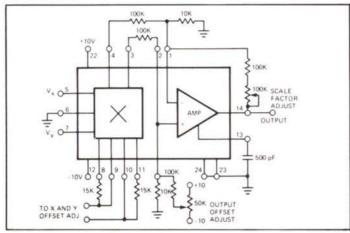

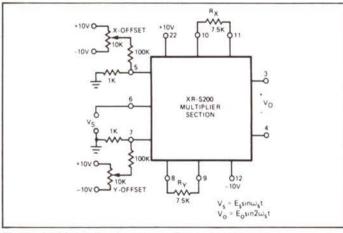

| MULTIPLIER SECTION: See                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Figure 2, R <sub>X</sub> | $= R_y = 15k$ | Pins 1, 2, 6    | , 23, 24 Ground | led.                                           |  |

| Output Offset Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          | ±40           | ±120            | mV              | $V_x = V_y = 0, V_{i0} =  V_3 - V_4 $          |  |

| Input Bias Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          | 5             | 15              | μA              | Measured at pins 5 and 7                       |  |

| Input Offset Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          | 0.1           | 1.0             | μA              | Measured at pins 5 and 7                       |  |

| Linearity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                          |               |                 |                 |                                                |  |

| (Output error, %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          | 1.0           |                 | %               | $-5 < V_x < +5$ , $V_y = \pm 5V$               |  |

| of full scale)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          | 1.5           |                 | %               | $-5 < V_y < +5, V_x = \pm 5V$                  |  |

| Scale Factor, KM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          | 0.1           |                 | _               | $K_{M} = 25/R_{x}R_{y}$ (Adjustable)           |  |

| Input Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.3                      | 1.0           |                 | MΩ              | f = 20 Hz, Measured at pins 5 and 7            |  |

| 3 dB Bandwidth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3                        | 6             |                 | MHz             | $C_{\rm L} \leq 5  \rm pF$                     |  |

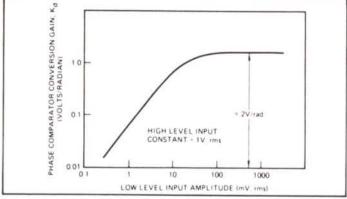

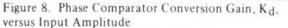

| Phase detection B.W.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 50                       | 100           |                 | MHz             | $R_{x} = R_{y} = 0$                            |  |

| Differential Output Swing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ±4                       | ±6            |                 | V p-p           | Measured across pins 3 and 4                   |  |

| Output Impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |               |                 |                 | incustica across prilo 5 and 1                 |  |

| Single Ended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          | 6             |                 | kΩ              | Measured at pins 3 and 4                       |  |

| Differential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          | 12            |                 | kΩ              | measured at pins 5 and 4                       |  |

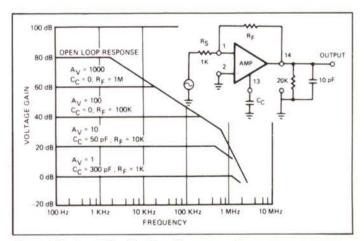

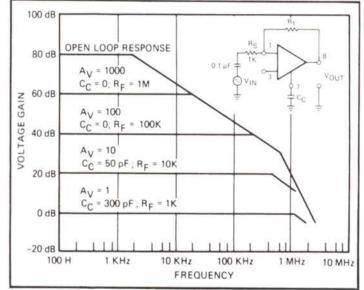

| OPERATIONAL AMPLIFIER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SECTION: (               |               | 0 and 11 R      |                 | 50 pF                                          |  |

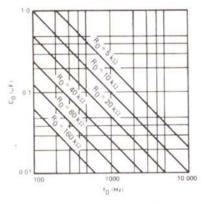

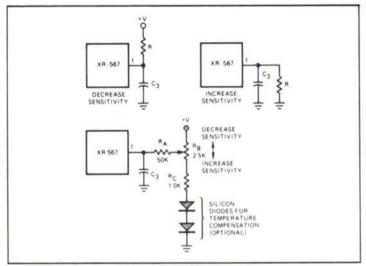

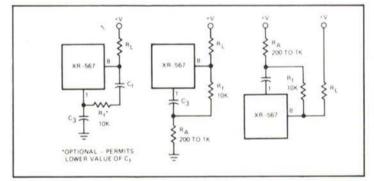

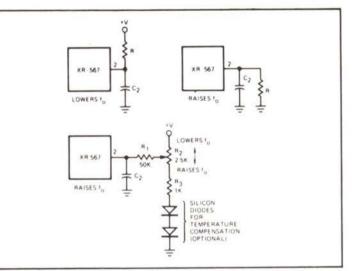

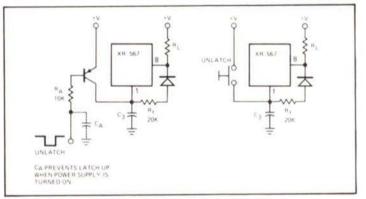

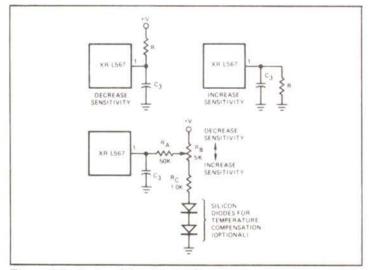

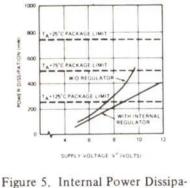

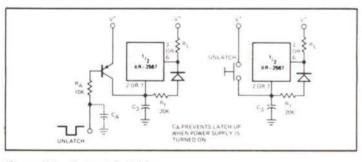

| Input Bias Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          | 0.08          | 0.5             | 1               |                                                |  |